# An Operational Approach to Library Abstraction under Relaxed Memory Concurrency

ABHISHEK KR SINGH, Tel Aviv University, Israel ORI LAHAV, Tel Aviv University, Israel

Concurrent data structures and synchronization mechanisms implemented by expert developers are indispensable for modular software development. In this paper, we address the fundamental problem of library abstraction under weak memory concurrency, and identify a general library correctness condition allowing clients of the library to reason about program behaviors using the specification code, which is often much simpler than the concrete implementation. We target (a fragment of) the RC11 memory model, and develop an equivalent operational presentation that exposes knowledge propagation between threads, and is sufficiently expressive to capture library behaviors as totally ordered operational execution traces. We further introduce novel access modes to the language that allow intricate specifications accounting for library internal synchronization that is not exposed to the client, as well as the library's demands on external synchronization by the client. We illustrate applications of our approach in several examples of different natures.

CCS Concepts: • Theory of computation  $\rightarrow$  Concurrency; Operational semantics; Program verification; • Software and its engineering  $\rightarrow$  Semantics; Software verification; Abstraction, modeling and modularity.

Additional Key Words and Phrases: Relaxed memory consistency, Concurrent objects, Linearizability, Library abstraction

#### **ACM Reference Format:**

Abhishek Kr Singh and Ori Lahav. 2023. An Operational Approach to Library Abstraction under Relaxed Memory Concurrency. *Proc. ACM Program. Lang.* 7, POPL, Article 53 (January 2023), 31 pages. https://doi.org/10.1145/3571246

## 1 INTRODUCTION

Library abstraction constitutes a powerful means to achieve modularity in software development. It allows expert library developers to write optimized implementations of common programming tasks, and "once and for all" establish that these implementations admit their corresponding specifications. In turn, users of these implementations, called *clients* of the library, may reason about program behaviors assuming only the libraries' specifications, with no understanding, or even no access, to the implementations. From a formal standpoint, a perquisite for applying library abstraction is to identify a condition that provably allows library developers to abstract away from a particular client program when verifying their implementations, while ensuring the soundness of client reasoning using the specifications in any (valid) client program.

In the case of sequential programs, library abstraction is straightforward: specifications may be given using pre- and post-conditions, and it is easy to establish the soundness of client reasoning that is based on them. Concurrent programs, however, require more attention. Assuming

Authors' addresses: Abhishek Kr Singh, Tel Aviv University, Israel, abhishek.uor@gmail.com; Ori Lahav, Tel Aviv University, Israel, orilahav@tau.ac.il.

This work is licensed under a Creative Commons Attribution 4.0 International License.

© 2023 Copyright held by the owner/author(s).

2475-1421/2023/1-ART53

https://doi.org/10.1145/3571246

an underlying sequentially consistent (SC) memory system [Lamport 1979], classical linearizability (w.r.t. some sequential specification) [Herlihy and Wing 1990] ensures refinement w.r.t. a sequential object [Filipović et al. 2010], and can be seen as a library abstraction condition. More recent approaches employ "code as specification" (see, e.g., [Gotsman and Yang 2011]), where implementations are specified using (simple) code, and library abstraction amounts to contextual refinement between two pieces of code. Linearizability can be seen as a particular instance of this approach, where specifications are obtained by wrapping a sequential implementation within a global lock [Bouajjani et al. 2015]. Furthermore, to make such specification formalism more useful, one often enriches the given programming language with special specification constructs, that are employed only in the specification code and are relatively easy to reason about (e.g., atomic blocks in concurrent programs).

The current paper studies library abstraction under relaxed (a.k.a. weak) shared-memory concurrency. In particular, we consider a C11-style weak memory model with several kinds of memory-access modes (a.k.a. memory orderings), placed differently on the spectrum between efficient implementation (with an optimizing compiler targeting a modern multicore hardware) and strong consistency guarantees. The infamous complexity of programming under such a model makes library abstraction indispensable. In particular, library abstraction allows clients to use the programming guarantees supplied by the model, e.g., clients should be able to rely on the synchronization induced by a library (such as a lock library) for ensuring data-race freedom in their programs, and then apply the model's guarantee that data-race free programs have strong semantics.

Remark 1. Like many formal verification frameworks for C11, we are unable to work with the original model, which allows unrestricted cycles in the union of 'program order' and 'reads-from', and thus exhibits "out-of-thin-air" behaviors and fails to provide the most basic data-race-freedom guarantee. We follow [Boehm and Demsky 2014] and its formalization in the RC11 model in [Lahav et al. 2017] to conservatively disallow all such cycles. This entails a certain performance penalty for maintaining the load-store order between relaxed accesses [Ou and Demsky 2018]. We also note that the fragment of the RC11 handled in this paper lacks release/acquire fences and sequentially consistent accesses, which are left to future work.

Our main contribution is a correctness condition for libraries that provably ensures (contextual) refinement between implementations and their respective specifications under the weak memory model, with several distinctive properties:

- Our proposed condition is based on *totally ordered execution traces* of the library in question (a decision motivated below). Accordingly, we present a novel equivalent operational version of the (originally) declarative memory model, and use it in the correctness condition.

- To account for various restrictions that libraries may impose on their clients (e.g., refrain from data races between two specific methods), our result supports rich library calling policies, and refinement is conditioned on the client's adherence to the calling policy. Importantly, whether a program adheres to the policy or not is checked against the library specification, which allows the application of the abstraction theorem by the client without any knowledge of the implementation.

- Our specification language allows simple *lock-based* specifications of libraries that do not provide synchronization guarantees for their clients, and dually of libraries that rely on the client for performing the synchronization between library calls. For that matter, we introduce a novel access mode to the programming language (and memory model).

We illustrate the application of our approach for an RCU synchronization mechanism which we specify by relying solely on locks (§8.1), as well as for a relaxed concurrent queue object that does not expose its internal synchronization to its clients (§8.2). We also derive a (local) data-race-freedom guarantee for the memory model as an instance of library abstraction (§8.3).

Outline. This paper is organized as follows. In §2 we present an informal overview of the challenges we address and our solutions. In §3 we define concurrent programs and their semantics independent of a memory model. In §4 we present the memory model semantics, which we call dRC11 (d for 'declarative'), as a fragment of RC11 extended with novel constraints for the new access modes. In §5 we present an operational version of the memory model, which we call pRC11 (p for 'propagation'), that is needed for defining the library correctness condition. In §6 we introduce the notions required to formulate the library abstraction theorem. In §7 we state and prove the main theorem. In §8 we demonstrate applications of the abstraction theorem (which can assist in understanding the crux of the abstraction theorem even before reading the more technical material in Section 3 to 7). We discuss the relation to other work in §9 and conclude in §10. The *full version* of this paper available in [Singh and Lahav 2022] contains additional detailed proofs.

## 2 KEY CHALLENGES AND IDEAS

We outline the main challenges and the key ideas in our solutions. We keep the discussion and examples informal, leaving the formal development to later sections.

# 2.1 Library Correctness Criterion

The main challenge lies in establishing a library correctness condition that will ensure contextual refinement between a library specification  $L^{\#}$  (given as code) and its implementation L under weak memory semantics. Naturally, such condition should consider each object in isolation and avoid quantification over all possible clients. Moreover, we opt for an *operational* condition that, like standard linearizability, is based on totally ordered histories generated by the object in question. The latter desideratum is in contrast with previous work on library specifications in (R)C11 [Batty et al. 2013; Raad et al. 2019] and adaptations of linearizability to weak memory concurrency (see, e.g., [Dongol et al. 2018]), which employ multiple partial orders in their correctness criteria. We believe that an operational approach, based on *one* total timeline, may be more intuitive for users (also considering informal arguments), and will allow easier adoption of standard techniques and tools that were applied before to verify refinement between transition systems (see e.g., our initial experiment with the FDR refinement checker in §8.1).

While having an operational correctness criterion may seem contradicting to the fact that standard weak memory formulations, e.g., (R)C11, are *declarative* (a.k.a. axiomatic memory models), unlike previous work (e.g., [Batty et al. 2013]), we consider this to be only a superficial matter. Indeed, declarative specifications of models that forbid "reads from the future" (i.e., impose acyclicity of the union of the 'program order' and the 'read-from' relations; called an 'in-order' semantics in [Cho et al. 2021]) can be equally characterized as operational memory models: the states consist of the current execution trace ordered by multiple partial order relations as needed, and transitions are only between *consistent* states as specified by the consistency condition of the declarative model (see, e.g., the RAG transition system for the release/acquire fragment of C11 in [Lahav and Margalit 2019]). More concise (and possibly more intuitive) formulations of such semantics may use timestamps and views, and the equivalence to the "operationalized" declarative model is witnessed by a standard forward simulation relation (see, e.g., [Kaiser et al. 2017; Kang et al. 2017]).

Now, operational semantics (in particular, operationalized versions of declarative models), naturally give rise to a set of *library histories*, and allow the application of standard linearizability. For that matter, one considers a "most general client" program that invokes the library methods in the most general way expected by the library. Then, the set of library histories consists of all sequences of invocations (with the values of the arguments) and responses (with the returned values) of the library methods by different threads that are obtained in operational traces of that client. Under SC,

inclusion of the sets of histories between two libraries may serve as a library abstraction condition (i.e., if every history of a library L is also a history of  $L^{\#}$ , then L refines  $L^{\#}$ ).

Aiming to apply a similar condition, following previous work on abstraction under TSO [Burckhardt et al. 2012] and under non-volatile memory [Khyzha and Lahav 2022], we observe that under weak memory semantics, inclusion of sets of histories is generally *unsound* as a library correctness condition.<sup>1</sup> Next, we provide a simple (contrived) example of this issue.

*Example 2.1.* Consider a library L with two methods foo and bar and the following specification (here and henceforth we assume that all variables are initialized to 0):

```

\texttt{foo}(): \quad \texttt{store}(\texttt{x}, \texttt{1}, \texttt{rel}); \\ \texttt{return}(); \\ \\ \texttt{bar}(): \quad \texttt{a} := \texttt{load}(\texttt{x}, \texttt{acq}); \\ \texttt{return}(\texttt{a}); \\

```

Suppose that the library enforces a policy on its clients: (1) foo and bar must be called *exactly once* in *different* threads; and (2) bar must be called *after* foo in the execution order. For example, the following program adheres to this call policy:

The accesses to y ensure that in the generated traces the call to bar indeed appears only after foo returns. Nevertheless, speaking in C11 terminology, since these accesses are relaxed (as annotated by rlx mode), they do *not* induce a *happens-before* order between the calls, and thus, following the specification, the read from x inside bar may return 0 (the initial value) or 1. Accordingly, a "naive" library developer may attempt to efficiently implement L as follows (where  $\oplus$  denotes a non-deterministic choice):

```

\mathtt{foo}(): \quad \mathtt{return}(); \\ \\ \mathtt{bar}(): \quad \mathtt{return}(0) \oplus \mathtt{return}(1); \\

```

Is this implementation correct? In histories of the most general client of L that respects the library's calling policy (i.e., in histories generated by executing the above program) one cannot observe a difference between the implementation and the specification. But, nevertheless, contextual refinement does not hold (so the implementation cannot be considered correct) for two different reasons illustrated by the following client programs:

The annotated behaviors in both examples are allowed when the suggested implementation of foo and bar is used, but disallowed when the specification is used. Indeed, in the example on the left, since the specification ensures release/acquire synchronization when bar returns 1 (via the rel and acq annotations in the accesses to x), the write to z happens-before the read from z, and in this case the model disallows the read from z to observe the overwritten initial value. In turn, in the example on the right, since the *client* uses release/acquire accesses, the write in foo happens-before the read in bar, which similarly ensures that the read from x cannot observe the initial value.

To address this challenge, we need to make library histories more expressive, so we can avoid the (SC) pitfall that identifies the execution order and the synchronization order. Concretely, in the

<sup>&</sup>lt;sup>1</sup>Interestingly, it follows from our result that for a language that employs *only* RC11-style relaxed accesses, inclusion of sets of histories is a sound condition (like it is for SC). Such a language is, however, too weak to be considered useful.

example above, we need to expose the facts that: (1) bar returning 1 *entails* a happens-before relation from *the call of* foo to *the return of* bar; and (2) bar returning 0 *forbids* a happens-before relation from *the return of* foo to *the call of* bar. What does that mean in operational terms without talking about the happens-before partial order between call and return actions? Our solution consists of the following:

- We introduce a novel operational semantics of the memory model and show that it is equivalent to the original declarative model. The operational semantics makes *knowledge propagation* between threads explicit. Roughly speaking, an access that is executed by one thread is first unknown to the other threads, and later non-deterministically propagates to each other threads. Access modes impose certain constraints on the propagation order and the ability to read from (locally) unknown events. In the simplest case—for programs with only release/acquire accesses—the propagation order has to follow the program order and reads can only read from known writes.

- We include propagation of method invocations and responses in the memory trace and, in turn, in library histories. These steps have no effect on the outcomes of the operational semantics (i.e., what values can be read and when), but they serve as crucial "markers" in library history, making histories expressive enough for validating contextual refinement given the inclusion of the sets of histories. In other words, we keep the inclusion of the sets of library histories as the correctness criterion, and recover its soundness by including appropriate markers (call and return propagation among different threads) in the histories.

In particular, revisiting the example above, the proposed implementation will have a history in which the propagation of the call marker of foo is after the return of bar but bar returns 1; as well as a history in which the propagation of the return marker of foo is before the call of bar but bar returns 0. Both histories are impossible for the specification, so library correctness does not hold.

# 2.2 Specification under Relaxed Memory Concurrency

A second challenge that we address is related to specification of libraries that expose weak behaviors. A straightforward approach to specifying concurrent data structures is to take a simple sequential implementation of the data structure, and wrap every operation inside a per-object lock. In fact, correctness according to the classical linearizability criterion [Herlihy and Wing 1990] is equivalent to refinement with respect to such lock-based specifications [Bouajjani et al. 2015; Filipović et al. 2010]. Since a lock entails a total order on all operations, the resulting specification is typically easy to understand and enables reasoning similar to reasoning about sequential programs.

This approach, however, has major shortcomings under relaxed memory concurrency, as it identifies the execution order with the synchronization order, which is only justified assuming SC. For instance, consider the following program that uses a concurrent queue (inspired by [Mével and Jourdan 2021]):

Assuming a lock-based specification of the queue, the client may easily conclude that the annotated behavior (a = 1 and b = 0, where 0 is the initial value of x and the queue is initially empty) is impossible. Indeed, the fact that the dequeue operation returned the enqueued value entails that the lock of the dequeue operation must have been acquired after the lock of the enqueue operation was released. In turn, since locks necessarily provide release/acquire synchronization, the write to x happens-before the read from x, and thus the read cannot observe the overwritten initial value. Now, while the implementation of a queue may provide such synchronization guarantees for its client, it is also possible that the queue is implemented using efficient C11 relaxed accesses,

and thus comes with weaker guarantees that do not allow the client to rely on library-induced synchronization (so the accesses to x above are racy and a = 1 but b = 0 is possible). In that case the lock-based specification would be too strong.

We note that such weak guarantees do not imply that the queue is not "linearizable": there may still exist a total order on all queue operations that agrees with the execution order (which can be any total order extending the union of the program order and the reads-from relation), and the queue exhibits FIFO behavior w.r.t. that order. A weak queue may be useful transferring elements of base types, whereas, in order to be used for transferring ownership via pointers, the client is responsible to appropriately place fences before and after invoking the weak queue methods.

Remark 2. While release/acquire synchronization may seem natural between enqueue and dequeue of the same element, the lock-based specification implies synchronization also in other cases, which may or may not be supplied (the queue studied in [Mével and Jourdan 2021] provides a case in point). For example, a client relying on a lock-based specification can deduce that the following annotated outcomes are all disallowed (where  $\bot$  denotes an empty queue):

```

\begin{aligned} x &:= 1; \\ q.enqueue(1); & \quad | & b := q.dequeue; \ \# 1 \\ q.enqueue(1); & \quad | & c := q.dequeue; \ \# 2 \end{aligned} \end{aligned} \end{aligned} \quad \begin{aligned} x &:= 1; \\ a &:= q.dequeue; \ \# 1 \\ b &:= x; \ \# 0 \end{aligned}

```

Accordingly, the challenge lies in identifying specification constructs that can be used instead of standard locks and be sufficiently flexible to account for different synchronization guarantees for the client. Ideally, like locks, they should allow straightforward reasoning about the library behaviors. We observe that existing concurrency models, C11 in particular, lack such constructs.

To address this challenge, we propose to extend the language with specialized instructions. Concretely, we identify that there is a range of possible guarantees that lie between C11's release/acquire accesses (which provide synchronization) and relaxed accesses (which do not), and introduce a novel type of memory accesses that lies on this spectrum. Roughly speaking, these memory accesses, which we call *partial release/acquire*, ensure synchronization only for certain variables (see §4 for the formal definition).<sup>2</sup> C11's release/acquire accesses can be seen as partial release/acquire accesses that ensure synchronization for *all* variables, whereas C11's relaxed accesses can be seen as partial release/acquire accesses that do *not* ensure synchronization for *any* variable.

Partial release/acquire accesses can be used to construct locks that provide synchronization *only* for library variables, and these special locks can be used to specify libraries with weak synchronization guarantees. In particular, in the queue example above, locks implemented by *partial* release/acquire accesses would behave just like standard locks from library perspective, but will not allow the clients to rely on their induced synchronization. More generally, these accesses allow a library-internal release/acquire synchronization, which is needed for correct behaviors of the library, but is considered invisible from the point of view of the client.

## 3 CONCURRENT PROGRAMS: SYNTAX AND MEMORY-INDEPENDENT SEMANTICS

In this section we begin to present the formal preliminaries for our results. As standard in memory models, it is convenient to break the semantics into: a *program* semantics (a.k.a. thread subsystem) and a *memory* semantics. Next, we focus on the program part, presenting syntax (§3.1), semantics (§3.2), and the synchronization with a (parametric) memory system (§3.3).

<sup>&</sup>lt;sup>2</sup>We generally require libraries and clients to operate on different "address spaces" and never access the same shared variable. Lifting this simplifying assumption (e.g., as was done for SC in [Gotsman and Yang 2013]) is beyond our current scope.

# 3.1 Program Syntax

We employ a simple programming language, which supports the distinction between clients and libraries variable spaces.<sup>3</sup> We use the following domains (and metavariables ranging over them):

In particular, as we will see below, every memory access is to a particular variable in a particular variable space (like address spaces in operating systems); registers are thread-local variables; and the name main is reserved for non-library operations. Memory instructions have access modes (a.k.a. memory orderings), which determine their "strength" (na for non-atomics, rlx for relaxed, prel/pacq for partial release/acquire, and rel/acq for release/acquire). We also assume a relation  $\Box$  that orders modes according to their strength (following the left-to-right enumeration of the sets Mod<sub>R</sub> and Mod<sub>W</sub> above).

The language provides the following constructs, inspired by C11 atomics:

- Expressions are constructed with arithmetic and boolean operations over registers and values. We use *e* to range over expressions, and leave the exact expression grammar parametric.

- Thread local instructions (which do not interact with the shared-memory system):

- Assignments of the form r := e, used for storing an expression e in a register r.

- Conditionals of the form if e goto  $n_1 \mid ... \mid n_m$  (where  $n_1, ..., n_m \in \mathbb{N}$ ), used to non-deterministically jump to some program counter among  $\{n_1, ..., n_m\}$  when e evaluates to non-zero or, otherwise, skipping.

- Additional local instructions (standard loop constructs, unconditional non-deterministic choice, etc.). Below, we will use such instructions in our examples, and their semantics should be clear.

- Shared-memory single accesses:

- Write (a.k.a. store) instructions to memory of the form  $store(X, x, e, o_W)$  for storing into a shared variable x in space X the value that e evaluates to with access mode  $o_W$ .

- Read (a.k.a. load) instructions from memory of the form  $r := load(X, x, o_R)$  for loading the value from a shared variable x in space X into a register r with access mode  $o_R$ .

- Read-modify-write (RMW) instructions:

- Fetch-and-add (FAA) instructions of the form  $r := FADD(X, x, e, o_R, o_W)$  for atomically incrementing a variable x in space X by the value of e with read mode  $o_R$  and write mode  $o_W$ .

- Compare-and-swap (CAS) instructions of the form  $r := CAS(X, x, e_R, e_W, o_R, o_W, o_R^{fail})$ . This instruction atomically loads the value from x in space X into r, compares it to the value  $e_R$ , and overwrites it by the value of  $e_W$  in case if the loaded value coincides with the value  $e_R$ . The load part will have mode  $o_R$  if comparison succeeds and  $o_R^{fail}$  otherwise; and the store part (if it happens) has mode  $o_W$ .

- Library interaction:  $\mathtt{call}(f)$  for calling a method f and  $\mathtt{return}$  for returning to the caller. For simplicity, we do not provide any argument passing mechanism and we will use the full register store for that matter. (If needed, each component may store the values it needs in the memory, and reload them later on.)

To construct programs we introduce three syntactic categories, each of which builds on the previous one:

<sup>&</sup>lt;sup>3</sup>The partition to variable spaces is only needed to support the "partial release/acquire" access mode in library specifications, and can be completely ignored for specifications without such accesses.

- *Instruction sequences* represent the (sequential) implementation of each method (including main). Formally, an instruction sequence *I* is a function from a non-empty finite domain of the form  $\{0, ..., n\}$  (representing the possible program counters) to the set of instructions. We say that an instruction sequence is *flat* if it does not include call(\_) instructions.

- Sequential programs consist of a "main" method accompanied with implementations of every method  $f \in F$ . Formally, a sequential program sPr is a function assigning an instruction sequence to every  $f \in \{\text{main}\} \cup F$ . To avoid modeling a call stack and simplify the framework, we require that sPr(f) is a flat instruction sequence for every  $f \in F$ .

- *Concurrent programs*, which we often call *programs*, are top-level parallel compositions of sequential programs, all accompanied by the same method implementations. Formally, a (concurrent) program Pr is a mapping assigning a sequential program to every  $\tau \in Tid$ , with  $Pr(\tau)(f) = Pr(\pi)(f)$  for every  $\tau, \pi \in Tid$  and  $f \in F$ .

In our examples, we often write instruction sequences as sequences of instructions delimited by ";", and concurrent programs using ' $\parallel$ ' between the main method of each thread. We also refer to the program threads as  $T_1, T_2, ...$  following their left-to-right order in the program listing.

## 3.2 Program Semantics

We give semantics to the syntactic objects above using labeled transition systems.

Definition 3.1. A labeled transition system (LTS) is a tuple  $A = \langle \Sigma, Q, q_0, T \rangle$ , where  $\Sigma$  is a set of transition labels, Q is a set of states,  $q_0 \in Q$  is the initial state, and  $T \subseteq Q \times \Sigma \times Q$  is a set of transitions. We denote by  $A.\Sigma$ , A.Q,  $A.Q_0$ , and A.T the components of an LTS A. We write  $q \xrightarrow{\sigma} q'$  to denote a transition  $\langle q, \sigma, q' \rangle$ ,  $\xrightarrow{\sigma}_A$  for the relation  $\{\langle q, q' \rangle \mid q \xrightarrow{\sigma} q' \in A.T\}$ , and  $\to_A$  for  $\bigcup_{\sigma \in \Sigma} \xrightarrow{\sigma}_A$ . For a sequence  $t \in A.\Sigma^*$ , we write  $\xrightarrow{t}_A$  for the composition  $\xrightarrow{t(1)}_A$ ; ...;  $\xrightarrow{t(|t|)}_A$ . A sequence  $t \in A.\Sigma^*$  such that  $A.Q_0 \xrightarrow{t}_A q$  for some  $q \in A.Q$  is called a trace of A. We denote by traces(A) the set of all traces of A. A state  $Q \in A.Q$  is called reachable in A if  $A.Q_0 \xrightarrow{t}_A q$  for some  $t \in Taces(A)$ . For a trace t and a set  $\Theta \subseteq \Sigma$  of transition labels, we write  $t|_{\Theta}$  for the longest subsequence of t over  $\Theta$ .

Next, we define the LTSs induced by instruction sequences, sequential programs, and concurrent programs. We often identify the syntactic objects with the LTS they induce (e.g., when writing expressions like *sPr*.Q for a sequential program *sPr*). The transition labels of these LTSs feature *action labels*, which represent the interactions that a program may have with the memory.

Definition 3.2. An action label l takes one of the following forms: a read  $R(X, x, v_R, o_R)$ , a write  $W(X, x, v_W, o_W)$ , a read-modify-write  $RMW(X, x, v_R, v_W, o_R, o_W)$ , a call  $CALL(f, \phi)$ , and a return  $RET(\phi)$ , where  $X \in Space$ ,  $x \in Loc$ ,  $v_R, v_W$ ,  $\in Val$ ,  $o_R \in Mod_R$ ,  $o_W \in Mod_W$ ,  $f \in F$ , and  $\phi : Reg \to Val$ . We denote by Lab the set of all action labels. The functions typ, sp, loc,  $val_R$ ,  $val_W$ ,  $rad_W$ ,  $val_W$ ,  $rad_W$ ,  $val_W$

Next, we define the LTS induced by an instruction sequence.

Definition 3.3. An instruction sequence state is a pair  $\langle pc, \phi \rangle$ , where  $pc \in \mathbb{N}$ , called program counter, stores the current instruction pointer inside the sequence, and  $\phi : \text{Reg} \to \text{Val}$ , called local store, records the values of the registers. Local stores are extended to apply on expressions in the standard way. The LTS induced by an instruction sequence I is an LTS over instruction sequence states with:  $\text{Lab}_{\epsilon} \triangleq \text{Lab} \cup \{\epsilon\}$  as the set of transition labels (that is, the set of all action labels extended with  $\epsilon$  for silent transitions);  $\langle 0, \phi_{\text{Init}} \rangle$  where  $\phi_{\text{Init}} \triangleq \lambda r$ . 0 as the initial state; and the transitions as given in Fig. 1 (additional thread local instructions can be standardly added).

$$I(pc) = r := e \\ \frac{\phi' = \phi[r \mapsto \phi(e)]}{\langle pc, \phi \rangle \xrightarrow{\epsilon}_{I} \langle pc + 1, \phi' \rangle} \qquad \frac{I(pc) = \text{if } e \text{ goto } n_1 + \dots + n_m}{\phi(e) \neq 0 \implies pc' \in \{n_1, \dots, n_m\}} \qquad \frac{I(pc) = r := \text{load}(X, x, o_R)}{\langle pc, \phi \rangle \xrightarrow{\epsilon}_{I} \langle pc + 1, \phi' \rangle} \qquad \frac{I(pc) = r := \text{load}(X, x, o_R)}{\langle pc, \phi \rangle \xrightarrow{\epsilon}_{I} \langle pc', \phi \rangle} \qquad \frac{I(pc) = r := \text{load}(X, x, o_R)}{\langle pc, \phi \rangle \xrightarrow{l}_{I} \langle pc + 1, \phi' \rangle} \qquad \frac{I(pc) = r := \text{load}(X, x, o_R)}{\langle pc, \phi \rangle \xrightarrow{l}_{I} \langle pc + 1, \phi' \rangle} \qquad \frac{I(pc) = r := \text{load}(X, x, o_R)}{\langle pc, \phi \rangle \xrightarrow{l}_{I} \langle pc + 1, \phi' \rangle} \qquad \frac{I(pc) = r := \text{load}(X, x, o_R)}{\langle pc, \phi \rangle \xrightarrow{l}_{I} \langle pc + 1, \phi' \rangle} \qquad \frac{I(pc) = r := \text{load}(X, x, o_R)}{\langle pc, \phi \rangle \xrightarrow{l}_{I} \langle pc + 1, \phi' \rangle} \qquad \frac{I(pc) = r := \text{load}(X, x, o_R)}{\langle pc, \phi \rangle \xrightarrow{l}_{I} \langle pc + 1, \phi' \rangle} \qquad \frac{I(pc) = r := \text{load}(X, x, o_R)}{\langle pc, \phi \rangle \xrightarrow{l}_{I} \langle pc + 1, \phi' \rangle} \qquad \frac{I(pc) = r := \text{load}(X, x, o_R)}{\langle pc, \phi \rangle \xrightarrow{l}_{I} \langle pc + 1, \phi' \rangle} \qquad \frac{I(pc) = r := \text{load}(X, x, o_R)}{\langle pc, \phi \rangle \xrightarrow{l}_{I} \langle pc + 1, \phi' \rangle} \qquad \frac{I(pc) = r := \text{load}(X, x, o_R)}{\langle pc, \phi \rangle \xrightarrow{l}_{I} \langle pc + 1, \phi' \rangle} \qquad \frac{I(pc) = r := \text{load}(X, x, o_R)}{\langle pc, \phi \rangle \xrightarrow{l}_{I} \langle pc + 1, \phi' \rangle} \qquad \frac{I(pc) = r := \text{load}(X, x, o_R)}{\langle pc, \phi \rangle \xrightarrow{l}_{I} \langle pc + 1, \phi' \rangle} \qquad \frac{I(pc) = r := \text{load}(X, x, o_R)}{\langle pc, \phi \rangle \xrightarrow{l}_{I} \langle pc + 1, \phi' \rangle} \qquad \frac{I(pc) = r := \text{load}(X, x, o_R)}{\langle pc, \phi \rangle \xrightarrow{l}_{I} \langle pc + 1, \phi' \rangle} \qquad \frac{I(pc) = r := \text{load}(X, x, o_R)}{\langle pc, \phi \rangle \xrightarrow{l}_{I} \langle pc + 1, \phi' \rangle} \qquad \frac{I(pc) = r := \text{load}(X, x, o_R)}{\langle pc, \phi \rangle \xrightarrow{l}_{I} \langle pc + 1, \phi' \rangle} \qquad \frac{I(pc) = r := \text{load}(X, x, o_R)}{\langle pc, \phi \rangle \xrightarrow{l}_{I} \langle pc + 1, \phi' \rangle} \qquad \frac{I(pc) = r := \text{load}(X, x, o_R)}{\langle pc, \phi \rangle \xrightarrow{l}_{I} \langle pc + 1, \phi' \rangle} \qquad \frac{I(pc) = r := \text{load}(X, x, o_R)}{\langle pc, \phi \rangle \xrightarrow{l}_{I} \langle pc + 1, \phi' \rangle} \qquad \frac{I(pc) = r := \text{load}(X, x, o_R)}{\langle pc, \phi \rangle \xrightarrow{l}_{I} \langle pc + 1, \phi' \rangle} \qquad \frac{I(pc) = r := \text{load}(X, x, o_R)}{\langle pc, \phi \rangle \xrightarrow{l}_{I} \langle pc + 1, \phi' \rangle} \qquad \frac{I(pc) = r := \text{load}(X, x, o_R)}{\langle pc, \phi \rangle \xrightarrow{l}_{I} \langle pc + 1, \phi' \rangle} \qquad \frac{I(pc) = r := \text{load}(X, x, o_R)}{\langle pc, \phi \rangle \xrightarrow{l}_{I} \langle pc + 1, \phi' \rangle} \qquad \frac{I(pc) = r := \text{load}(X, x, o_R)}{\langle pc, \phi \rangle \xrightarrow{l}_{I} \langle pc + 1, \phi' \rangle} \qquad \frac{I(pc) = r := \text{load}(X$$

Fig. 1. Transitions of LTS induced by an instruction sequence

Recall that program semantics is separate from memory semantics, which is why the read and RMW transitions in Fig. 1 can observe any value. It is only important that each transition that interacts with the memory announces itself in the transition label. The call(\_) and return instructions are not handled at the level of instruction sequences, but receive special semantics at the level of sequential programs, as defined next.

Definition 3.4. A sequential program state is a tuple  $q = \langle pc, \phi, pc_s, f \rangle$ , where:  $\langle pc, \phi \rangle$  is an instruction sequence state storing the state of the sequence currently running;  $pc_s \in \mathbb{N} \cup \{\bot\}$ , called the stored program counter, is used to remember the program position to jump to when the current instruction sequence returns  $(pc_s = \bot \text{ means that the main method is currently running})$ ; and  $f \in F \cup \{\text{main}\}$ , called the active method, tracks the method that is currently running. We denote by  $q.pc_s$ ,  $q.\phi$ ,  $q.pc_s$ , and q.f the components of a sequential program state q.

Definition 3.5. The LTS induced by a sequential program sPr is given by:

- The set of transition labels is  $Lab_{\epsilon} \times (F \cup \{main\})$ . The functions lab and method respectively retrieve the action label (or  $\epsilon$ ) and method name of a transition label. All functions on action labels (typ, sp, loc, ...) are lifted to sequential program transition labels in the obvious way.

- The states are sequential program states, as defined in Def. 3.4.

- The initial state is  $\langle 0, \phi_{\mathsf{Init}}, \bot, \mathtt{main} \rangle$ .

- The transitions are given by:

$$\frac{f \in \{\mathtt{main}\} \cup \mathsf{F} \qquad \langle pc, \phi \rangle \xrightarrow{l_{\epsilon}}_{\mathit{SPr}(f)} \langle pc', \phi' \rangle}{\langle pc, \phi, pc_{\mathsf{S}}, f \rangle \xrightarrow{l_{\epsilon}, f}_{\mathit{SPr}} \langle pc', \phi', pc_{\mathsf{S}}, f \rangle} \\ sPr(\mathtt{main})(pc) = \mathtt{call}(f) \qquad \qquad sPr(f)(pc) = \mathtt{return} \\ l = \mathtt{CALL}(f, \phi) \qquad \qquad l = \mathtt{RET}(\phi) \\ \hline \langle pc, \phi, \bot, \mathtt{main} \rangle \xrightarrow{l,\mathtt{main}}_{\mathit{SPr}} \langle 0, \phi, pc + 1, f \rangle \qquad \langle pc, \phi, pc_{\mathsf{S}}, f \rangle \xrightarrow{l, f}_{\mathit{SPr}} \langle pc_{\mathsf{S}}, \phi, \bot, \mathtt{main} \rangle}$$

The first transition, which applies for any method (main or other), lifts the instruction-sequence transition to the level of sequential programs. The second transition passes control from the main method to some other method, jumping the program counter to the first instruction and storing the return point (pc + 1). Finally, the third transition passes control back using the stored return point. (We do not need to record a call stack since we assume that sPr(f) is flat for every  $f \in F$ .)

Finally, the LTS induced by a concurrent program interleaves the thread transitions.

Definition 3.6. A (concurrent) program state  $\overline{p}$  is a mapping assigning a sequential program state to every  $\tau \in \text{Tid}$ . The LTS induced by a program Pr is an LTS over program states, with:  $\text{ProgLab} \triangleq \text{Tid} \times \text{Lab}_{\epsilon} \times (\mathsf{F} \cup \{\texttt{main}\})$  as the set of transition labels;  $\overline{p}_{\mathsf{lnit}} \triangleq \lambda \tau \cdot \langle 0, \phi_{\mathsf{lnit}}, \bot, \mathtt{main} \rangle$  as the initial state; and the following transitions:

$$\frac{\overline{p}(\tau) \xrightarrow{l_{\epsilon}, f} p_{r(\tau)} q'}{\overline{p} \xrightarrow{\tau, l_{\epsilon}, f} p_{r} \overline{p}[\tau \mapsto q']}$$

Below, for a program transition label  $\alpha \in \text{ProgLab}$ , the functions tid, lab, and method respectively retrieve the thread identifier  $(\tau)$ , the action label (or  $\epsilon$ ) ( $l_{\epsilon}$ ), and the method name (f) of  $\alpha$ . Functions on action labels (typ, sp, loc, ...) are lifted to program transition labels in the obvious way.

# 3.3 Synchronizing Programs and Memories

To give semantics to programs running under a particular memory model, we synchronize the transitions of a program Pr with a memory system. For now, we leave the memory system parametric, and assume it is represented by some LTS  $\mathcal{M}$  whose set of transition labels consists of non-silent program transition labels (elements of Tid  $\times$  Lab  $\times$  (F  $\cup$  {main})) as well as a (disjoint) set  $\mathcal{M}.\Theta$  of internal memory actions (which we use later for non-deterministic propagation of knowledge between threads).

Definition 3.7. The composition of a program Pr and a memory system  $\mathcal{M}$ , denoted by  $Pr\bowtie \mathcal{M}$ , is the LTS whose transition labels are the elements of ProgLab  $\cup$   $\mathcal{M}.\Theta$ ; states are pairs  $\langle \overline{p}, M \rangle \in Pr.Q \times \mathcal{M}.Q$ ; initial state is  $\langle \overline{p}_{\text{Init}}, \mathcal{M}.q_0 \rangle$ ; and transitions are given by:

$$\frac{\alpha \in \mathsf{Tid} \times \mathsf{Lab} \times (\mathsf{F} \cup \{\mathtt{main}\})}{\frac{\overline{p} \xrightarrow{\alpha} p_r \ \overline{p}' \qquad M \xrightarrow{\alpha}_{\mathcal{M}} M'}{\langle \overline{p}, M \rangle \xrightarrow{\alpha} p_{r\bowtie \mathcal{M}} \langle \overline{p}', M' \rangle}} \qquad \frac{\alpha \in \mathsf{Tid} \times \{\varepsilon\} \times (\mathsf{F} \cup \{\mathtt{main}\})}{\frac{\overline{p} \xrightarrow{\alpha} p_r \ \overline{p}'}{\partial p_r p_r p'}} \qquad \frac{\alpha \in \mathcal{M}.\Theta}{\frac{\alpha}{\partial p_r \bowtie \mathcal{M}} \langle \overline{p}', M' \rangle} \qquad \frac{\overline{p} \xrightarrow{\alpha}_{\mathcal{M}} \mathcal{M}'}{\langle \overline{p}, M \rangle \xrightarrow{\alpha}_{\mathcal{M}} \langle \overline{p}', M' \rangle}$$

The above transitions are "synchronized transitions" of Pr and  $\mathcal{M}$ , using the labels to decide what to synchronize on. Both the program and the memory take the same step for transition labels that are common to both LTSs, only the program steps for transition labels that are program internal (i.e., with  $lab(\alpha) = \epsilon$ ) and only the memory steps for transition labels that are memory internal.

*Example 3.8.* The most well-known memory system is the one of sequential consistency, denoted here by SC. This memory system simply tracks the most recent value written to each variable, and has no internal transitions (SC. $\Theta = \emptyset$ ). Formally, it is defined by SC.Q  $\triangleq$  (Space × Loc)  $\rightarrow$  Val, SC.q<sub>0</sub>  $\triangleq$   $\lambda X$ , x. 0, and  $\rightarrow$  SC is given by:

$$\begin{array}{c} l = \mathsf{R}(X,x,v_{\mathsf{R}},\_) \\ \underline{m(X,x) = v_{\mathsf{R}}} \\ \underline{m} \xrightarrow{\tau,l,f} \\ \underline{m} \xrightarrow{\tau,l,f} \\ \mathsf{SC} \ m \end{array} \qquad \begin{array}{c} l = \mathsf{W}(X,x,v_{\mathsf{W}},\_) \\ \underline{m' = m[\langle X,x \rangle \mapsto v_{\mathsf{W}}]} \\ \underline{m} \xrightarrow{\tau,l,f} \\ \mathsf{SC} \ m' \end{array} \qquad \begin{array}{c} l = \mathsf{RMW}(X,x,v_{\mathsf{R}},v_{\mathsf{W}},\_,\_) \\ \underline{m(X,x) = v_{\mathsf{R}}} \\ \underline{m' = m[\langle X,x \rangle \mapsto v_{\mathsf{W}}]} \\ \underline{m' = m[\langle X,x \rangle \mapsto v_{\mathsf{W}}]} \\ \underline{m} \xrightarrow{\tau,l,f} \\ \mathsf{SC} \ m' \end{array} \qquad \begin{array}{c} \mathsf{typ}(l) \in \{\mathsf{CALL},\mathsf{RET}\} \\ \underline{m} \xrightarrow{\tau,l,f} \\ \mathsf{SC} \ m' \end{array}$$

## 4 THE dRC11 MEMORY MODEL

In this section we introduce the weak memory model that we assume in this paper. This model, which we call dRC11, is a declarative (a.k.a. axiomatic) model forming an extension of (a fragment of) the RC11 model [Lahav et al. 2017] with specialized semantics for the novel prel/pacq accesses.

NOTATION 4.1 (RELATIONAL NOTATIONS). Given a (binary) relation R, dom(R) and codom(R) denote its domain and codomain, and  $R^2$ ,  $R^+$ , and  $R^*$  denote its reflexive, transitive, and reflexive-transitive closures. The inverse of a relation R is denoted by  $R^{-1}$ , and the (left) composition of two

relations  $R_1$  and  $R_2$  is denoted by  $R_1$ ;  $R_2$ . We denote by [A] the identity relation on a set A. In particular, [A]; R;  $[B] = R \cap (A \times B)$ . When A is finite, we write  $[a_1, ..., a_n]$  instead of  $[\{a_1, ..., a_n\}]$ .

We start by defining *execution graphs*. Their nodes, called *events*, represent memory accesses, and their directed edges are of different kinds: *program order* represents the order imposed by the program; *reads-from* mapping maps each read event to the write event it obtains its value from; and *modification order* (a.k.a. *coherence order*) provides a total order on the writes to every variable. The precise definitions are given next.

Definition 4.2. An event e is a tuple  $\langle \tau, s, l, f \rangle$ , where  $\tau \in \text{Tid} \uplus \{\bot\}$ , called the event's thread identifier ( $\bot$  is used for initialization events);  $s \in \mathbb{N}$ , called the event's serial identifier;  $l \in \text{Lab}$ , called the event's label (as defined in Def. 3.2), and  $f \in F \cup \{\text{main}\}$ , called the event's method. The functions tid, sn, lab, and method return the thread identifier ( $\tau$ ), identifier (s), action label (s), and method of an event (s). All functions on action labels (typ, sp, loc, ...) are lifted to events in the obvious way. We denote by E the set of all events, and define the following subsets:

```

R \triangleq \{e \in E \mid \mathsf{typ}(e) \in \{\mathsf{R}, \mathsf{RMW}\}\} \qquad W \triangleq \{e \in E \mid \mathsf{typ}(e) \in \{\mathsf{W}, \mathsf{RMW}\}\} \qquad \mathsf{RMW} \triangleq \mathsf{R} \cap \mathsf{W} \mathsf{CALL} \triangleq \{e \in E \mid \mathsf{typ}(e) = \mathsf{CALL}\} \qquad \mathsf{RET} \triangleq \{e \in E \mid \mathsf{typ}(e) = \mathsf{RET}\} \qquad \mathsf{CR} \triangleq \mathsf{CALL} \cup \mathsf{RET}

```

We employ subscripts and superscripts to restrict sets of events to certain properties, e.g.,  $W_X = \{w \in W \mid \operatorname{sp}(w) = X\}$ ,  $R_{X,x}^{\supseteq \operatorname{pacq}} = \{r \in R \mid \operatorname{sp}(r) = X \land \operatorname{loc}(r) = x \land \operatorname{mod}_W(r) \supseteq \operatorname{pacq}\}$ ,  $\operatorname{CALL}_F = \{e \in \operatorname{CALL} \mid \operatorname{callee}(e) \in F\}$ ,  $\operatorname{RET}_F = \{e \in \operatorname{RET} \mid \operatorname{method}(e) \in F\}$ ,  $\operatorname{CR}_F = \operatorname{CALL}_F \cup \operatorname{RET}_F$ , and  $E^\tau = \{e \in E \mid \operatorname{tid}(e) = \tau\}$  for any  $E \subseteq E$ . The set Init of *initialization events* is given by:

```

Init \triangleq \{ \langle \bot, 0, W(X, x, 0, rlx), main \rangle \mid X \in Space, x \in Loc \}.

```

*Definition 4.3.* An execution graph G is a tuple (E, po, rf, mo), where:

- E is a finite set of events, such that Init  $\subseteq E$  and  $tid(e) \neq \bot$  for every  $e \in E \setminus Init$ .

- po is a program order for E, that is:  $po = (\biguplus_{\tau \in \mathsf{Tid}} po_{\tau}) \uplus (\mathsf{Init} \times (E \setminus \mathsf{Init}))$ , for some relations  $po_{\tau}$ , such that each  $po_{\tau}$  is a strict total order on  $E^{\tau}$ .

- *rf* is a *reads-from relation for E*, that is a relation on *E* satisfying:

- If  $\langle w, r \rangle \in rf$ , then  $w \in W$  and  $r \in R$ .

- If  $\langle w, r \rangle \in rf$ , then sp(w) = sp(r), loc(w) = loc(r), and  $val_W(w) = val_R(r)$ .

- $-w_1 = w_2$  whenever  $\langle w_1, r \rangle, \langle w_2, r \rangle \in rf$  (each read reads from at most one write).

- $-E \cap R \subseteq codom(rf)$  (each read reads from some write).

- mo is a modification order for E, that is:  $mo = \biguplus_{X \in Space, x \in Loc} mo_{X,x}$ , for some relations  $mo_{X,x}$ , such that each  $mo_{X,x}$  is a strict total order on  $E \cap W_{X,x}$ .

We denote the components of G by G.E, G.po, G.rf, and G.mo. For any set  $E' \subseteq E$ , we write G.E' for  $G.E \cap E'$  (e.g.,  $G.W = G.E \cap W$ ).

To formally associate execution graphs with programs we use a memory system called FG (for "free graphs"), whose states are execution graphs. This system allows *all* possible program transitions, while recording them in its state, which is the current execution graph with (almost) arbitrary reads-from and modification order relations.

Definition 4.4. The memory system FG is the LTS whose transition labels are program transition labels (i.e., there are not any internal memory actions); states are execution graphs; initial state is  $G_{\text{Init}}$ , defined by  $G_{\text{Init}}$ .  $E \triangleq \text{Init}$  and  $G_{\text{Init}}$ .  $X \triangleq \emptyset$  for every other component of G; and transitions are given in Fig. 2.

The transitions of FG are based on helper notations used to extend an execution graph *G* with a fresh event *e* at the end of the executing thread. For memory accesses, it requires to pick a write

$$\begin{array}{ll} \text{WRITE/READ/RMW} & \text{typ}(l) \in \{\text{W, R, RMW}\} & e = \text{NextEvent}(G.\text{E}, \tau, l, f) \\ w \in G.W_{\text{sp}(e),\text{loc}(e)} & e \in \text{R} \implies \text{val}_{\text{W}}(w) = \text{val}_{\text{R}}(e) \\ \hline & G' = \text{Add}(G, e, w) \\ \hline & G \xrightarrow{\tau, l, f}_{\text{FG}} G' \\ \end{array} \qquad \begin{array}{ll} \text{CALL/RETURN} \\ \text{typ}(l) \in \{\text{CALL, RET}\} \\ e = \text{NextEvent}(G.\text{E}, \tau, l, f) \\ G' = \text{Add}(G, e, \tau, l, f) \\ \hline & G' = \text{Add}(G, e, \tau, l, f) \\ \hline & G \xrightarrow{\tau, l, f}_{\text{FG}} G' \\ \end{array}$$

Fig. 2. Transitions of FG system for generating all candidate execution graphs

event w in G, called the *write-predecessor* of e, that is: (1) the rf-source of e if e is a read; (2) the mo-immediate predecessor of e if e is a write; and (3) both the rf-source and the mo-immediate predecessor of e if e is an RMW. For that matter, we employ the following notations:

NOTATION 4.5. Given a set E of events,  $\tau \in \text{Tid}$ ,  $l \in \text{Lab}$ , and  $f \in F$ , NextEvent $(E, \tau, l, f)$  denotes the event with thread identifier  $\tau$ , label l, method f, and a minimal fresh serial identifier w.r.t. E, that is: NextEvent $(E, \tau, l, f) \triangleq \langle \tau, s, l, f \rangle$ , where  $s = \min\{n \in \mathbb{N} \mid \langle \tau, n, l, f \rangle \notin E\}$ .

NOTATION 4.6. For an execution graph G and events e and w, Add(G, e, w) denotes the tuple  $\langle E', po', rf', mo' \rangle$ , where:

$$E' = G.E \cup \{e\} \qquad po' \triangleq G.po \cup ((G.E^{tid(e)} \cup Init) \times \{e\})$$

$$rf' = \begin{cases} G.rf \cup \{\langle w, e \rangle\} & e \in \mathbb{R} \\ G.rf & otherwise \end{cases} \qquad mo' = \begin{cases} G.mo \cup dom(G.mo^?; [w]) \times \{e\} \\ \cup \{e\} \times codom([w]; G.mo) \end{cases} \qquad e \in \mathbb{W}$$

$$G.mo \qquad otherwise$$

Similarly, for an execution graph G and event e, Add(G,e) denotes the tuple  $\langle E', po', G.rf, G.mo \rangle$ , where E' and po' are defined as above.

In the sequel, it will be useful to note that all execution graphs generated by FG when synchronized with a given program satisfy the following well-formedness property:

Definition 4.7. An execution graph G is well-formed if the following hold for every  $f \in F$ :

- $[\{e \in E \mid \mathsf{method}(e) \neq f\}]$ ;  $G.\mathsf{po}$ ;  $[\{e \in E \mid \mathsf{method}(e) = f\}] \subseteq G.\mathsf{po}^?$ ;  $[\mathsf{CALL}_{\{f\}}]$ ;  $G.\mathsf{po}$ .

- $[\{e \in \mathsf{E} \mid \mathsf{method}(e) = f\}]$ ;  $G.\mathsf{po}$ ;  $[\{e \in \mathsf{E} \mid \mathsf{method}(e) \neq f\}] \subseteq G.\mathsf{po}^2$ ;  $[\mathsf{RET}_{\{f\}}]$ ;  $G.\mathsf{po}$ .

PROPOSITION 4.8. If  $\langle \overline{p}, G \rangle$  is reachable in  $Pr \bowtie FG$  for some program Pr, then G is well-formed.

Now, to filter for *consistent* graphs among all candidate execution graphs generated by FG for a given program, we define several derived relations (some parametrized by  $X \in Space$ ):

```

G.\mathsf{fr} \triangleq (G.\mathsf{rf}^{-1}; G.\mathsf{mo}) \setminus [\mathsf{E}] (from-read, a.k.a. read-before)

G.\mathsf{sw}_{\mathsf{base}} \triangleq [\mathsf{W}^{\mathsf{rel}}]; G.\mathsf{rf}^+; [\mathsf{R}^{\mathsf{acq}}] (global synchronization)

G.\mathsf{sw}_X \triangleq [\mathsf{W}_X^{\exists \mathsf{prel}}]; G.\mathsf{rf}^+; [\mathsf{R}_X^{\exists \mathsf{pacq}}] (per-space synchronization)

G.\mathsf{hb}_X \triangleq (G.\mathsf{po} \cup G.\mathsf{sw}_{\mathsf{base}} \cup G.\mathsf{sw}_X)^+ (per-space happens-before)

```

The fr relation is standard in weak memory models [Alglave et al. 2014], relating every read (or RMW) to subsequent writes (or RMWs) as dictated by rf and mo (every write w that is mo-after the rf-source of a read r is fr-after r). The sw<sub>base</sub> and sw<sub>X</sub> relations formally capture synchronization: sw<sub>base</sub> is for "global" synchronization which is formed by reads-from edges between rel and acq accesses (just like in C11 [Lahav et al. 2017]), whereas sw<sub>X</sub> is for "space-internal" synchronization that affects only accesses to space X and is formed by reads-from edges in space X between prel

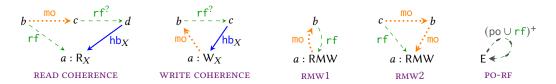

Fig. 3. Illustration of forbidden patterns in dRC11

and pacq. The use of rf<sup>+</sup> (rather than just rf) is for supporting release sequences as in C11, which ensures the synchronization between a release write w and an acquire read r also if there is chain of reads-from edges between them  $(\langle w, u_1 \rangle, \langle u_1, u_2 \rangle, \dots, \langle u_{n-1}, u_n \rangle, \langle u_n, r \rangle \in rf$  where  $u_1, \dots, u_n$ are RMWs, which can be relaxed).<sup>4</sup> Finally, paths composed of the program order (po) and the  $sw_{base}$  and  $sw_X$  relations form the per-space happens-before relation, which again refines the C11 happens-before relation (defined as  $(G.po \cup G.sw_{base})^+$ ).

Using the above definitions, the consistency of an execution graph is defined as follows.

*Definition 4.9.* An execution graph *G* is dRC11-consistent if the following hold:

- For every  $X \in \text{Space}$ ,  $[R_X]$ ; G.fr;  $G.\text{rf}^?$ ;  $G.\text{hb}_X$  is irreflexive. (READ COLLE)

(WRITE COHERENCE)

(RMW1)

- For every  $X \in \text{Space}$ ,  $[W_X]$ ; G.mo;  $G.\text{rf}^?$ ;  $G.\text{hb}_X$  is irreflexive.

- *G.*mo ; *G.*rf is irreflexive. (RMW1)

- *G*.fr ; *G*.mo is irreflexive. (RMW2)

- $G.po \cup G.rf$  is acyclic. (PO-RF)

These constraints, depicted in Fig. 3, are variants of the ones in (R)C11, where the only essential difference is in the coherence constraints that here use  $G.hb_X$  for restricting accesses to  $X.^5$  The RMW1 and RMW2 constraints are needed for ensuring the right behavior of RMWs including their atomicity. The PO-RF constraint is an addition of RC11 on top of C11, which is a conservative solution to the "out-of-thin-air" problem that arises if po∪rf-cycles are allowed [Batty et al. 2015; Kang et al. 2017].

The next example demonstrates the role of the coherence constraints:

Example 4.10. Consider the following standard "message-passing" litmus test (parametric in the space *Y* and the access modes  $o_W$ ,  $o_R$ ):

```

a: W(X, x, 1, rlx) \setminus c: R(Y, y, 1, o_R)

```

The annotated behavior is disallowed only if the synchronization on y (in space Y) is visible for the read of x (in space X). This will be the case only if (1)  $o_W = \text{rel}$  and  $o_R = \text{acq}$ ; or (2)  $o_W \supseteq \text{prel}$ ,  $o_R \supseteq pacq$ , and Y = X (i.e., the four accesses are to the same space). (In particular, if  $Y \neq X$ , then only  $o_W = rel$  and  $o_R = acq$  would forbid the annotated behavior.) To see how this follows from

<sup>&</sup>lt;sup>4</sup>Another component of C11's release sequence, which allows forming synchronization using a relaxed write po-after a release write to the same location, was omitted from the standard in C++20. (See https://en.cppreference.com/w/cpp/atomic/ memory order [Accessed July 2022].)

<sup>&</sup>lt;sup>5</sup>There are some presentational differences w.r.t. the model in [Lahav et al. 2017]: (1) RC11 uses two events related by an rmw-edge to represent RMWs, so RMW1 is not needed and RMW2 has a different formulation (called Atomicity in [Lahav et al. 2017]); and (2) RC11 uses the "extended coherence order" (eco) which allows it to merge both coherence constraints.

the coherence constraints, note that these conditions are needed to ensure  $\langle b, c \rangle \in \mathsf{sw}_{\mathsf{base}} \cup \mathsf{sw}_{\mathsf{X}}$ , which in turn implies  $\langle a, d \rangle \in \mathsf{hb}_{\mathsf{X}}$ . Now, since  $\langle init, a \rangle \in \mathsf{po} \subseteq \mathsf{hb}_{\mathsf{X}}$ , write coherence ensures that  $\langle init, a \rangle \in \mathsf{mo}$ , and so  $\langle d, a \rangle \in \mathsf{fr}$ . In turn, read coherence disallows  $\mathsf{hb}_{\mathsf{X}}$  from a to d.

By connecting the definition of candidate execution graphs for a given program (using the FG system) and dRC11-consistency, we define the allowed program behaviors under dRC11 (more precisely, possible reachable program states).

Definition 4.11. A program state  $\overline{p}$  is reachable for a program Pr under dRC11 if  $\langle \overline{p}, G \rangle$  is reachable in  $Pr \bowtie FG$  for some dRC11-consistent execution graph G.

Finally, again following (R)C11, data races on non-atomics are considered as programming errors (so non-atomic accesses can be heavily optimized by the hardware and the compiler). Accordingly, we define racy execution graphs and racy programs.

Definition 4.12. Two events  $e_1$  and  $e_2$  form a *race* in an execution graph G, if  $e_1, e_2 \in G.W \cup G.R$ ,  $e_1 \neq e_2$ ,  $\operatorname{sp}(e_1) = \operatorname{sp}(e_2)$ ,  $\operatorname{loc}(e_1) = \operatorname{loc}(e_2)$ ,  $|\{e_1, e_2\} \cap W| \geq 1$ ,  $|\{e_1, e_2\} \cap \mathsf{E}^{\mathsf{na}}| \geq 1$ , and  $\langle e_1, e_2 \rangle \notin G.\mathsf{hb}_{\operatorname{sp}(e_1)} \cup G.\mathsf{hb}_{\operatorname{sp}(e_1)}^{-1}$ . An execution graph G is *racy* if some two events form a race in G.

Definition 4.13. A program Pr is racy under dRC11 if  $\langle \overline{p}, G \rangle$  is reachable in  $Pr \bowtie FG$  for some program state  $\overline{p}$  and racy dRC11-consistent execution graph G.

## 5 THE OPERATIONAL MEMORY SYSTEM: pRC11

In this section we introduce an operational version of the dRC11 memory model, called pRC11, which exposes knowledge propagation steps as internal memory steps, and is particularly suitable for library abstraction.

Since dRC11-consistency is prefix-closed w.r.t. pourf [Kokologiannakis et al. 2017], dRC11 can be easily made operational by adapting the LTS FG (Def. 4.4) to require dRC11-consistency after each step of the execution graph generation (rather than one time at the end). However, following §2.1, we opt for a more elaborate model with explicit point-to-point  $propagation\ transitions$  marking the steps in which some event of thread  $\tau$  becomes visible to another thread  $\pi$ . In particular, this allows us to observe the propagation of the call/return events in memory traces, which is essential in our definition of the library correctness condition in §7. We expose propagation transitions in traces of pRC11 as internal memory steps labeled with  $propagation\ labels$  as defined next.

Definition 5.1. A propagation label is a triple, denoted by  $p = \mathsf{EP}(e,\tau,X)$ , where  $e \in \mathsf{E}$  (propagated event),  $\tau \in \mathsf{Tid} \setminus \{\mathsf{tid}(e)\}$  (destination thread identifier), and  $X \in \mathsf{Space}$  (destination space). We use  $\mathsf{E}$ ,  $\mathsf{ptid}$  and  $\mathsf{psp}$  to retrieve the components  $(e,\tau,\mathrm{and}\ X,\mathrm{respectively})$  of a propagation label p. All functions on events and action labels (tid, typ...) are lifted to propagation labels in the obvious way. We denote by PLab the set of all propagation labels.

Then, the pRC11 memory system is defined as follows.

Definition 5.2. The pRC11 memory system is an LTS whose set of transition labels is ProgLab  $\cup$  PLab (i.e., pRC11. $\Theta$  = PLab); states are pairs of the form  $M = \langle G, K \rangle$ , where G is an execution graph and K is a knowledge mapping for G, that is a function in Tid  $\rightarrow$  Space  $\rightarrow \mathcal{P}(G.E)$ ; initial state is  $M_{\text{lnit}} \triangleq \langle G_{\text{lnit}}, K_{\text{lnit}} \rangle$ , where  $K_{\text{lnit}} \triangleq \lambda \tau$ .  $\lambda X$ . Init ( $G_{\text{lnit}}$  is defined in Def. 4.4); and transitions are as given in Fig. 4.

In addition to the current execution graph G, pRC11's states record a *knowledge mapping* K that records for each thread  $\tau$  and space X all events that have already propagated to  $\tau$  for space X (as well as all events associated with actions executed by  $\tau$  itself). We refer to the set  $K(\tau)(X)$  as the X-knowledge of thread  $\tau$ .

```

\begin{aligned} & \text{typ}(l) \in \{\text{W}, \text{R}, \text{RMW}\} \quad e = \text{NextEvent}(G.E, \tau, l, f) \quad X = \text{sp}(e) \\ & w \in G.W_{X, \text{loc}(e)} \quad e \in \text{R} \implies \text{val}_{\mathbb{W}}(w) = \text{val}_{\mathbb{R}}(e) \\ & w \notin dom(G.\text{mo} ; G.\text{rf}^? ; [K(\tau)(X)]) \quad e \in \mathbb{W} \implies w \notin dom(G.\text{rf} ; [\text{RMW}]) \\ & e \in \text{R}^{\text{pacq}} \implies dom(G.\text{rf}^* ; [w]) \subseteq K(\tau)(X) \quad e \in \text{R}^{\text{acq}} \implies \forall Y. \ dom(G.\text{rf}^* ; [w]) \subseteq K(\tau)(Y) \\ & G' = \text{Add}(G, e, w) \quad k' = \lambda Y. K(\tau)(Y) \cup \{e\} \quad K' = K[\tau \mapsto k'] \\ & \qquad \qquad \langle G, K \rangle \xrightarrow{\tau, l, f}_{\text{pRC11}} \langle G', K' \rangle \\ & \qquad \qquad \text{CALL/RETURN} \\ & \qquad \qquad \text{typ}(l) \in \{\text{CALL}, \text{RET}\} \quad e = \text{NextEvent}(G.E, \tau, l, f) \\ & \qquad \qquad \qquad G' = \text{Add}(G, e) \quad k' = \lambda Y. K(\tau)(Y) \cup \{e\} \quad K' = K[\tau \mapsto k'] \\ & \qquad \qquad \langle G, K \rangle \xrightarrow{\tau, l, f}_{\text{pRC11}} \langle G', K' \rangle \\ & \qquad \qquad PROPAGATE \\ & \qquad \qquad e \in G.E \setminus K(\tau)(X) \\ & \qquad \qquad e \in W_X^{\text{prel}} \cup W^{\text{rel}} \cup \text{CR} \implies (E_X \cup \text{CR}) \cap dom(G.\text{hb}_X ; [e]) \subseteq K(\tau)(X) \\ & \qquad \qquad k' = K(\tau)[X \mapsto K(\tau)(X) \cup \{e\}] \quad K' = K[\tau \mapsto k'] \\ & \qquad \qquad \qquad \langle G, K \rangle \xrightarrow{\text{EP}(e, \tau, X)}_{\text{pRC11}} \langle G, K' \rangle \end{aligned}

```

Fig. 4. Transitions of pRC11.

The WRITE/READ/RMW transition in Fig. 4 executes a memory access by thread  $\tau$ , by adding a corresponding event e to the current execution graph while imposing certain conditions on w, the write-predecessor of e. Intuitively, the main imposed condition,  $w \notin dom(G.mo; G.rf^?; [K(\tau)(X)])$ , requires that w is not overwritten by any other write that  $\tau$  is already aware of for the space of e. More precisely, if e is an access in space X, then  $\tau$  should not have in its X-knowledge any write that is mo-later than w or any read that reads from a write that is mo-later than w. In addition:

- If *e* is a write (or RMW), then *w* should not be already read by an RMW. This condition is needed to ensure the atomicity of RMWs (corresponds to RMW2 in Def. 4.9).

- If *e* is a read (or RMW) with acq or pacq mode, then *w* (the write that *e* reads from) has to be already present in the thread's knowledge: in its *X*-knowledge if *e* is pacq, or in *Y*-knowledge for all *Y* if *e* is acq. (Moreover, if *w* is an RMW, to account for release sequences, this should hold not only for *w*, but also for every event on the rf-chain entering *w*.)

Finally, every thread certainly knows about its own actions, so in addition to extending G, this step also extends the knowledge of  $\tau$  by adding the event e to all spaces.

The CALL/RETURN transition is simple: it adds a corresponding event e to the current execution graph and extends the knowledge of the executing thread to include e.

The Propagate transition is a non-deterministic internal memory step that extends the threads' knowledge. It picks some event e that is not in  $\tau$ 's X-knowledge and adds e to  $K(\tau)(X)$ . When e is a prel-write to space X, a rel-write (to any space), or a call or return marker, then the propagation of e to the X-knowledge of thread  $\tau$  can be done only after all accesses to X, as well as all call and return markers, that are G.hb $_X$ -before e have propagated to the X-knowledge of thread  $\tau$ . What is not constrained is equally important: for instance, relaxed writes can propagate "out-of-order".

Example 5.3. pRC11's transitions are best understood via the "message-passing" litmus test presented in Example 4.10. Consider first the case that  $o_W = \text{rel}$  and  $o_R = \text{acq}$ . Then, due to the constraints on acquire reads and release writes: (1) since the read of y is acquire, it has to read

from a write that is in T2's X-knowledge hold for every space X: and (2) since the write of y is release, this write can only propagate to the X-knowledge of  $T_2$  (for every X) after the po-earlier write to x has propagated there. This means that if the read of y retrieves 1, then  $T_2$  already has the write to x in its X-knowledge, so when later reading x it cannot read from the overwritten initial value. Similarly, if  $o_W = prel$ ,  $o_R = pacq$ , and Y = X, then, (i) and (ii) apply for X = X, and the same reasoning holds. Nevertheless, in every other case, T2 can read the overwritten initial value: because either (1) the read from y is too weak and it allows to read from an event that has not yet propagated to the thread's X-knowledge; or (2) the write to y is too weak and it can propagate to the thread's X-knowledge before the po-earlier write to X has propagated.

Example 5.4. Being equivalent to dRC11, pRC11 provides "per-location-SC" (a.k.a. coherence). As a concrete example,  $a = 1 \land b = 0$  in the following program on the right is disallowed.

To see this in pRC11, note that read events are also included in the threads' knowledge. Concretely, after executing the first read, the second thread has its own read cuting the first read, the second thread has its own read in its X-knowledge. Then, reading later from the (implicit) store(X, x, 1, rlx); store(X, x, 1, rlx); store(X, x, 1, rlx); store(X, x, 1, rlx); initialization write is forbidden by pRC11 since that write and the first read will be have G.mo; G.rf between them.

Remark 3. It is also instructive to consider a simplified fragment with only one variable space and without na/rlx accesses. In this fragment, we can simply talk about the knowledge of each thread (instead of the X-knowledge for each X), and observe that: reads by thread  $\tau$  can only read from writes that thread  $\tau$  already knows about; and the propagation order respects hb (in particular, it follows the program order). This actually makes the reads deterministic: they have to read-from the mo-latest write among all known writes to the relevant variable. The resulting model is similar to message passing models for causal consistency [Beillahi et al. 2021].

Based on the pRC11 memory system, we define reachable program states and racy programs.

Definition 5.5. A program state  $\overline{p}$  is reachable for a program Pr under pRC11 if  $\langle \overline{p}, \langle G, K \rangle \rangle$  is reachable in  $Pr \bowtie pRC11$  for some  $\langle G, K \rangle \in pRC11.Q$ . A program Pr is racy under pRC11 if  $\langle \overline{p}, \langle G, K \rangle \rangle$ is reachable in  $Pr \bowtie pRC11$  for some program state  $\overline{p}$  and  $\langle G, K \rangle \in pRC11.Q$  such that G is a racy execution graph (see Def. 4.12).

# Equivalence of pRC11 and dRC11

We state our equivalence result between pRC11 and dRC11, relating Def. 5.5 to Definitions 4.11 and 4.13.

Theorem 5.6 (Equivalence of the Models). A program state  $\bar{p}$  is reachable for a program Pr under dRC11 iff it is reachable for Pr under pRC11. Furthermore, Pr is racy under dRC11 iff it is racy under pRC11.

Next, we describe the main steps in the proof (the full proof is given in [Singh and Lahav 2022]). First, for the right-to-left directions, it suffices to establish the following invariants on reachable pRC11-states.

Definition 5.7. A knowledge mapping K is well-formed for an execution graph G if the following hold for every  $\tau \in \mathsf{Tid}$  and  $X \in \mathsf{Space}$ :

```

(1) G.E^{\tau} \subseteq K(\tau)(X).

(2) (\mathsf{E}_X \cup \mathsf{CR}) \cap \mathit{dom}(G.\mathsf{hb}_X; [(\mathsf{W}_X^{\mathsf{prel}} \cup \mathsf{W}^{\mathsf{rel}}) \cap K(\tau)(X)]) \subseteq K(\tau)(X).

(3) (\mathsf{E}_X \cup \mathsf{CR}) \cap dom(G.\mathsf{hb}_X; [\mathsf{E}^\tau]) \subseteq K(\tau)(X).

```

Proc. ACM Program. Lang., Vol. 7, No. POPL, Article 53. Publication date: January 2023.

PROPOSITION 5.8. If  $\langle G, K \rangle$  is reachable in pRC11, then K is well-formed for G.

LEMMA 5.9. If  $\langle G, K \rangle$  is reachable in pRC11, then G is dRC11-consistent.

For the converse, one starts with an dRC11-consistent execution graph G, and has to traverse its events (following the program order, so it can be syncronized with the program), and intersperse propagation actions to make it a valid trace of pRC11. To construct this traversal, we define the following relations, where  $P \triangleq \{p \in \mathsf{PLab} \mid \mathsf{E}(p) \in G.\mathsf{E}\}$ :

```

\begin{split} R_{\mathsf{prop}} &\triangleq \{\langle e, p \rangle \in G.\mathsf{E} \times P \mid \mathsf{E}(p) = e\} \\ T &\triangleq \{\langle p, p' \rangle \in P \times P \mid \begin{array}{c} \mathsf{ptid}(p) = \mathsf{ptid}(p') \wedge \mathsf{psp}(p) = \mathsf{psp}(p') \wedge \\ \langle \mathsf{E}(p), \mathsf{E}(p') \rangle \in [\mathsf{E}_{\mathsf{psp}(p)} \cup \mathsf{CR}] \; ; G.\mathsf{hb}_{\mathsf{psp}(p)} \; ; [\mathsf{W}^{\mathsf{prel}}_{\mathsf{psp}(p)} \cup \mathsf{W}^{\mathsf{rel}} \cup \mathsf{CR}] \} \\ R_{\mathsf{rfp}} &\triangleq \{\langle p, e \rangle \in P \times G.\mathsf{E} \mid \langle \mathsf{E}(p), e \rangle \in G.\mathsf{rf}^+ \wedge \mathsf{ptid}(p) = \mathsf{tid}(e) \wedge e \in \mathsf{R}^{\mathsf{pacq}}_{\mathsf{psp}(p)} \} \\ R_{\mathsf{rf}} &\triangleq \{\langle p, e \rangle \in P \times G.\mathsf{E} \mid \langle \mathsf{E}(p), e \rangle \in G.\mathsf{rf}^+ \wedge \mathsf{ptid}(p) = \mathsf{tid}(e) \wedge e \in \mathsf{R}^{\mathsf{acq}} \} \\ R_{\mathsf{fr}} &\triangleq \{\langle r, p \rangle \in G.\mathsf{E} \times P \mid \langle r, \mathsf{E}(p) \rangle \in G.\mathsf{fr} \; ; G.\mathsf{rf}^? \wedge \mathsf{ptid}(p) = \mathsf{tid}(r) \wedge \mathsf{psp}(p) = \mathsf{sp}(r) \} \\ R_{\mathsf{mo}} &\triangleq \{\langle w, p \rangle \in G.\mathsf{E} \times P \mid \langle w, \mathsf{E}(p) \rangle \in G.\mathsf{mo} \; ; G.\mathsf{rf}^? \wedge \mathsf{ptid}(p) = \mathsf{tid}(w) \wedge \mathsf{psp}(p) = \mathsf{sp}(w) \} \\ R &\triangleq G.\mathsf{po} \cup G.\mathsf{rf} \cup R_{\mathsf{prop}} \cup T \cup R_{\mathsf{rfp}} \cup R_{\mathsf{rf}} \cup R_{\mathsf{fr}} \cup R_{\mathsf{mo}} \end{split}

```

Then, the proof proceeds by showing that R is acyclic, and that every total order of  $G.E \cup P$  extending R induces a trace of pRC11. Indeed, the relations above are in one-to-one correspondence with the conditions in the steps of pRC11.

# **6 LIBRARIES AND THEIR CLIENTS**

In this section we list the necessary definitions for the library abstraction theorem, and state the key properties that are used in its proof.

**Client-library composition.** A library L is a function mapping a set  $dom(L) \subseteq F$  of method names to flat instruction sequences representing the method bodies. We only consider the case where libraries and their clients never access the same variable space. To formally define this syntactic restriction, we use the following notations for spaces used by libraries and their clients:

- Space(*I*) denotes the set of variable spaces mentioned in an instruction sequence *I*.

- For a library L,  $Space(L) \triangleq \bigcup_{f \in dom(L)} Space(L(f))$ .

- For a program Pr and a set  $F \subseteq F$ ,  $\operatorname{Space}(Pr \setminus F) \triangleq \bigcup_{\tau \in \operatorname{Tid}, f \in (F \cup \{\operatorname{main}\}) \setminus F} \operatorname{Space}(Pr(\tau)(f))$ . Then, client-library composition is defined as follows.

Definition 6.1. A library L is safe for a program Pr if  $\operatorname{Space}(L) \cap \operatorname{Space}(Pr \setminus dom(L)) = \emptyset$ . When L is safe for Pr, we write Pr[L] for the program obtained from Pr by setting  $Pr(\tau)(f) = L(f)$  for every  $\tau \in \operatorname{Tid}$  and  $f \in dom(L)$ .

Next, we observe that the safety condition above ensures that execution graphs generated by Pr[L] satisfy the following conditions relating the location spaces and the invoked methods of the graph events.

PROPOSITION 6.2. Let L be a library that is safe for a program Pr. Suppose that  $\langle \overline{p}, G \rangle$  is reachable in  $Pr[L] \bowtie FG$ . Then, the following hold for every  $e \in G.R \cup G.W$ :

- $If \operatorname{sp}(e) \in \operatorname{Space}(L)$ , then  $\operatorname{method}(e) \in dom(L)$ .

- If  $sp(e) \in Space(Pr \setminus dom(L))$ , then  $method(e) \notin dom(L)$ .

*Definition 6.3.* A set  $F \subseteq F$  is *encapsulated in an execution graph G* if for every  $e_1, e_2 \in G.R \cup G.W$  with method( $e_1$ ) ∈ F and method( $e_2$ ) ∉ F, we have  $sp(e_1) \neq sp(e_2)$ .

From Prop. 6.2, we obtain the following.

PROPOSITION 6.4. Let L be a library that is safe for a program Pr. If  $\langle \overline{p}, G \rangle$  is reachable in  $Pr[L] \bowtie FG$ , then dom(L) is encapsulated in G.

The notions of well-formedness and encapsulated set of methods are lifted to memory states in the obvious way:

Definition 6.5. Let  $M = \langle G, K \rangle$  be a memory state.

- $M = \langle G, K \rangle$  is well-formed if G is well-formed (Def. 4.7) and K is well-formed for G (Def. 5.7).

- F is encapsulated in M if it is encapsulated in G (Def. 6.3).

Since every reachable state in  $Pr[L] \bowtie pRC11$  is also reachable in  $Pr[L] \bowtie FG$ , the following is an immediate consequence of Propositions 4.8, 5.8 and 6.4.

PROPOSITION 6.6. Let L be a library that is safe for a program Pr. If  $\langle \overline{p}, M \rangle$  is reachable in  $Pr[L] \bowtie pRC11$ , then M is well-formed and dom(L) is encapsulated in M.

*Client-library program states.* We define the composition of a program state  $\overline{p}_{cl}$  representing a client state and a program state  $\overline{p}_{lib}$  representing a library state as follows.

Definition 6.7. The composition of two program states  $\overline{p}_{cl}$  and  $\overline{p}_{lib}$  w.r.t. a set  $F \subseteq F$ , denoted by  $\overline{p}_{cl}[F \mapsto \overline{p}_{lib}]$ , is given by:

$$\overline{p}_{\rm cl}[F \mapsto \overline{p}_{\rm lib}] \triangleq \lambda \tau. \begin{cases} \langle \overline{p}_{\rm lib}(\tau).{\sf pc}, \overline{p}_{\rm lib}(\tau).\phi, \overline{p}_{\rm cl}(\tau).{\sf pc}_{\rm s}, \overline{p}_{\rm cl}(\tau).{\sf f} \rangle & \overline{p}_{\rm cl}(\tau).{\sf f} \in F \\ \overline{p}_{\rm cl}(\tau) & \text{otherwise} \end{cases}$$

This definition uses  $\overline{p}_{cl}$  for threads that are not currently inside a method in F, and  $\overline{p}_{lib}$ , but with the stored program counter and active method of  $\overline{p}_{cl}$ , for threads that are inside a method in F.

*Histories*. Histories record the interactions between libraries and clients. Formally, a *history h* of a library L is a sequence of transition labels representing a call to a method of L, a return from a method of L, or propagation of these call and return events. To define the history induced by a program, we employ the following notations (for every  $F \subseteq F$ ):

$$\begin{aligned} \operatorname{Call}_F &\triangleq \{\alpha \in \operatorname{ProgLab} \mid \operatorname{typ}(\alpha) = \operatorname{CALL} \wedge \operatorname{callee}(\alpha) \in F\} \\ \operatorname{Ret}_F &\triangleq \{\alpha \in \operatorname{ProgLab} \mid \operatorname{typ}(\alpha) = \operatorname{RET} \wedge \operatorname{method}(\alpha) \in F\} \\ \operatorname{HLab}_F &\triangleq \operatorname{Call}_F \cup \operatorname{Ret}_F \cup \operatorname{CP}_F \cup \operatorname{RP}_F \end{aligned}$$

*Definition 6.8.* Let  $F \subseteq F$ . The *F-history* induced by a trace t of  $Pr \bowtie pRC11$  for some program Pr, denoted by  $H_F(t)$ , is given by  $H_F(t) \triangleq t|_{HLab_F}$ . This notion is extended to sets of traces in the obvious way. The set of *F-histories of a program* Pr, denoted by  $H_F(Pr)$ , is given by  $H_F(Pr) \triangleq H_F(traces(Pr \bowtie pRC11))$ .

*Client-library trace restrictions*. We extract library and client transitions from a given trace as follows.

Definition 6.9. For  $F \subseteq F$ , the *F*-restriction and the  $\overline{F}$ -restriction of a trace t of  $Pr \bowtie pRC11$ , denoted by  $t|_F$  and  $t|_{\overline{F}}$  (respectively), are given by:

$$t|_F \triangleq t|_{\{\alpha \in \mathsf{ProgLab} \cup \mathsf{PLab} \mid \mathsf{method}(\alpha) \in F\} \cup \mathsf{Call}_F \cup \mathsf{CP}_F} \qquad t|_{\overline{F}} \triangleq t|_{\{\alpha \in \mathsf{ProgLab} \cup \mathsf{PLab} \mid \mathsf{method}(\alpha) \notin F\} \cup \mathsf{Ret}_F \cup \mathsf{RP}_F}$$

Note that both the *F*-restriction and the  $\overline{F}$ -restriction of a trace t contain the *F*-history induced by t as a subsequence.

**Restricting memory states**. Similarly, we will need to restrict memory states to client/library, as defined next.

Definition 6.10. The restriction of an execution graph G w.r.t. a set  $E \subseteq E$ , denoted by  $G|_E$ , is defined by:  $G|_E.E \triangleq E \cup Init$  and  $G|_E.X \triangleq [G|_E.E]$ ; G.X;  $[G|_E.E]$  for every other component (i.e.,  $X \in \{po, rf, mo\}$ ).

Definition 6.11. The restriction of a memory state  $M = \langle G, K \rangle$  w.r.t. a set  $E \subseteq E$ , denoted by  $M|_E$ , is given by  $M|_E \triangleq \langle G|_E, K|_E \rangle$ , where  $K|_E \triangleq \lambda \tau. \lambda X. K(\tau)(X) \cap E$ .

*Definition 6.12.* Let  $F \subseteq F$ . The *F*-events and the  $\overline{F}$ -events denoted by  $E_F$  and  $E_{\overline{F}}$  (respectively), are given by:

$$\mathsf{E}_F \triangleq \{e \in \mathsf{E} \mid \mathsf{method}(e) \in F\} \cup \mathsf{CALL}_F \qquad \qquad \mathsf{E}_{\overline{F}} \triangleq \{e \in \mathsf{E} \mid \mathsf{method}(e) \notin F\} \cup \mathsf{RET}_F$$

The *F*-restriction and the  $\overline{F}$ -restriction of a memory state  $M = \langle G, K \rangle$ , denoted by  $M|_F$  and  $M|_{\overline{F}}$  (respectively), are given by  $M|_F \triangleq M|_{\mathsf{E}_F}$  and  $M|_{\overline{F}} \triangleq M|_{\mathsf{E}_{\overline{F}}}$ .