# AUTOMATED REASONING UNDER WEAK MEMORY CONSISTENCY

Thesis approved by the Department of Computer Science University of Kaiserslautern-Landau for the award of the Doctoral Degree Doctor of Natural Sciences (Dr. rer. nat.)

to

Michail Kokologiannakis

Date of Defense: 14.12.2023

| Dean:     | Prof. Dr. Christoph Garth     |

|-----------|-------------------------------|

| Reviewer: | Dr. Viktor Vafeiadis          |

| Reviewer: | Prof. Dr. Constantin Enea     |

| Reviewer: | Prof. Dr. Mohamed Faouzi Atig |

DE-386

Στην οιχογένειά μου, Γιάννη, Ελένη και Αλέξη

To my family, Yannis, Eleni and Alexis

\_\_\_\_

### ABSTRACT

Weak memory consistency models capture the outcomes of concurrent programs that appear in practice and yet cannot be explained by thread interleavings. Such outcomes pose two major challenges to formal methods. First, establishing that a memory model satisfies its intended properties (e.g., supports a certain compilation scheme) is extremely error-prone: most proposed language models were initially broken and required multiple iterations to achieve soundness. Second, weak memory models make verification of concurrent programs much harder, as a result of which there are no scalable verification techniques beyond a few that target very simple models.

This thesis presents solutions to both of these problems. First, it shows that the relevant metatheory of weak memory models can be effectively decided (sparing years of manual proof efforts), and presents Kater, a tool that can answer metatheoretic queries in a matter of seconds. Second, it presents GenMC, the first (and only) scalable stateless model checker that is parametric in the choice of the memory model, often improving the prior state of the art by orders of magnitude.

v

First and foremost, I would like to thank my advisor, Viktor Vafeiadis, who influenced my thinking in more ways than I could imagine. Guidance and technical skills aside, he taught me that what lies at the heart of high-quality research is the combination of abstraction, mathematical rigor, and the elegance of simplicity. A prime example of academic leadership, Viktor was always there, as a mentor and a friend. Thank you, Viktor, from the bottom of my heart.

Throughout my PhD, I was also very fortunate to be unofficially mentored by Rupak Majumdar. Rupak was an endless source of motivation through stimulating scientific discussions, continuous feedback on my research, but also encouraging words and witty remarks.

The work presented in this thesis would not have been possible without a number of wonderful collaborators: Constantin Enea, Dimitra Giannakopoulou, Vladimir Gladstein, Ilya Kaysin, Ori Lahav, Rupak Majumdar, Iason Marmanis, Evgenii Moiseenko, Azalea Raad, Xiowei Ren, and Kostis Sagonas. Most of the papers in this thesis were written in close collaboration with Iason Marmanis, Azalea Raad and Ori Lahav, with whom I immensely enjoyed working together.

I am thankful to Constantin Enea and Mohamed Faouzi Atig for reviewing the thesis; to Dimitra Giannakopoulou for hosting me in AWS and making San Francisco sound like "Agios Fragkiskos"; and to Kostis Sagonas for introducing me to the world of verification.

I am also indebted to the past and current members of the Software Analysis and Verification group for fostering a friendly and welcoming environment: Soham Chakraborty, Marko Doko, Aristotelis Koutsouridis, Iason Marmanis, Anton Podkopaev, Lovro Rožič, and particularly to Azalea Raad and Léo Stefanesco, with whom I shared an office for the first and second half of my PhD, respectively.

During my PhD journey, I was also very fortunate to be accompanied by a number of friends, old and new, in Germany and abroad. In lieu of a dedicated page in the thesis containing their names, I extend to each and every one of them a heartfelt "thank you". Special thanks to Amir Bahador, James, Ivan, Kaushik, Manuel, Maria, Nastaran, Rosa, Andriana, Vasilis and Zannis for their help in different times.

I thank my fiancée, Kyriaki, for her love, support and patience during the past few years.

Finally, I would like to thank my parents, Yannis and Eleni, and my brother, Alexis, for all the sacrifices they made so that I can pursue my studies. This thesis is dedicated to them, as a token of an otherwise ineffable gratitude.

## CONTENTS

| 1 | Intr                        | oduction                                          | 1  |

|---|-----------------------------|---------------------------------------------------|----|

|   | 1.1                         | Challenges of Weak Memory Consistency             | 1  |

|   | 1.2 Contributions           |                                                   |    |

|   | 1.3 Structure               |                                                   |    |

|   | 1.4 Publications and Impact |                                                   |    |

| 2 | Bacl                        | kground                                           | 7  |

|   | <b>2.</b> 1                 | Programming Language                              | 7  |

|   | 2.2                         | Execution Graphs                                  | 9  |

|   | 2.3                         | Weak Memory Consistency Models                    | 11 |

|   | 2.4                         | From Programs to Execution Graphs                 | 12 |

|   |                             | 2.4.1 Dependency-Tracking Models                  | 14 |

| I | Met                         | atheory                                           |    |

| 3 | Kat                         | ER: Automating Weak Memory Model Metatheory       | 19 |

|   | 3.1                         | Regular Languages and Finite State Automata       | 20 |

|   | 3.2                         | Kleene Algebra with Tests (KAT)                   | 21 |

|   | 3.3                         | Memory Models as KAT Constraints                  | 22 |

|   | 3.4                         | Adding Domain-specific Assumptions                | 23 |

|   |                             | 3.4.1 Extended Coherence Order                    | 23 |

|   |                             | 3.4.2 Release-Acquire Consistency                 | 26 |

|   | 3.5                         | Irreflexivity Implications                        | 27 |

|   | 3.6                         | Proving Memory-Model Equivalence                  | 29 |

|   |                             | 3.6.1 Coherence                                   | 30 |

|   |                             | 3.6.2 Total Store Ordering (TSO)                  | 31 |

|   | 3.7                         | C11 Compilation Results                           | 32 |

|   | 3.8                         | Other Metatheoretic Properties                    | 35 |

| 4 |                             | cking Execution Graph Consistency                 | 37 |

|   | 4.1                         | Optimized Consistency Checks for SC               | 38 |

|   | 4.2                         | Arbitrary Acyclicity Checks with KATER            | 38 |

|   |                             | 4.2.1 Checking Consistency in Linear Time         | 40 |

|   |                             | 4.2.2 Checking Consistency Incrementally          | 41 |

|   | 4.3                         | Approximating Coherence with Writes-Before        | 42 |

| Π | Veri                        | fication                                          |    |

| 5 | Gen                         | MC: Model Checking under Weak Memory Consistency  | 49 |

|   | 5.1                         | Requirement #1: No "Out of Thin Air"              | 50 |

|   | 5.2                         | Requirement #2: Prefix-closedness                 | 51 |

|   | 5.3                         | A First Example                                   | 52 |

|   | 5.4                         | Requirement #3: Extensibility                     | 54 |

|   |                             | 5.4.1 Defining the Extensibility Oracle $f_{ext}$ | 56 |

|   | 5.5                         | Read-Modify-Write Operations                      | 57 |

|   | 5.6                         | Shasha-Snir and Reads-From Equivalence            | 60 |

| 5.7 Dependency-Tracking Models |      |                                                 | 51       |

|--------------------------------|------|-------------------------------------------------|----------|

|                                | 5.8  | Algorithm                                       | 52       |

|                                |      | 5.8.1 Overview                                  | 52       |

|                                |      | 5.8.2 Adaptation for a Reads-From Equivalence 6 | 66       |

| 6                              | Tru  | St: Polynomial Memory Requirements for GenMC 6  | 67       |

|                                | 6.1  | Maximal Extensions                              | 58       |

|                                | 6.2  | Examples                                        | 69       |

|                                | 6.3  | Algorithm                                       | 71       |

|                                |      | 6.3.1 Overview                                  | 71       |

|                                |      | 6.3.2 Memory Requirements                       | 72       |

|                                |      |                                                 | 73       |

|                                | 6.4  |                                                 | 73       |

|                                | 6.5  |                                                 | 75       |

|                                | 5    |                                                 | 76       |

|                                |      | -                                               | 76       |

|                                |      | 5                                               | 76       |

|                                |      |                                                 | 77       |

| 7                              | Opt  |                                                 | ,<br>79  |

| /                              | 7.1  |                                                 | 79<br>79 |

|                                | /.1  | -                                               | 30       |

|                                |      | ,                                               | 32       |

|                                |      |                                                 | 35       |

|                                | 7.2  | -                                               | 36       |

|                                | 7.2  |                                                 | 37       |

|                                |      |                                                 | 38       |

|                                |      | -                                               |          |

|                                |      |                                                 | 39       |

|                                |      |                                                 | 91       |

|                                |      |                                                 | )2       |

|                                |      |                                                 | 94       |

|                                |      |                                                 | 96       |

|                                | 7.3  |                                                 | 98       |

|                                |      |                                                 | 98       |

|                                |      | 7.3.2 Futile Explorations                       |          |

| _                              | _    | 7.3.3 Algorithm                                 |          |

| 8                              |      | SEVERE: Model Checking for Persistency 10       | )5       |

|                                | 8.1  | Persistency Semantics                           | )6       |

|                                | 8.2  | A Naive Approach                                | - C      |

|                                | 8.3  | Recovery Observer                               | )8       |

|                                | 8.4  | Example 11                                      | lO       |

|                                | Teel | la <sup>e</sup> Frankration                     |          |

| III                            |      | ls & Evaluation                                 |          |

| 9                              | Tool |                                                 | 15       |

|                                | 9.1  | Kater                                           | -        |

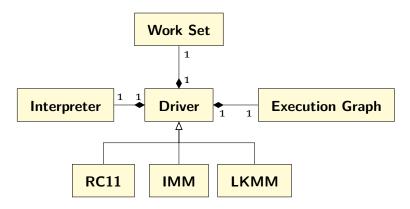

|                                | 9.2  | GenMC                                           | -        |

|                                |      |                                                 | 17       |

|                                |      | 9.2.2 Static Transformations                    | 18       |

| MC 126               |

|----------------------|

| 126                  |

| ng for GenMC . 127   |

| odel Requirements129 |

| 131                  |

| 131                  |

| 132                  |

| 132                  |

| 135                  |

| mption 141           |

| ization 144          |

| 146                  |

|                      |

| 151                  |

| 151                  |

| NMC 153              |

| nted 153             |

| fferent Models . 155 |

|                      |

| 159                  |

|                      |

|                      |

|                      |

|                      |

|                      |

| scape 165            |

| 169                  |

|                      |

|                      |

| 171                  |

| scape                |

## LIST OF FIGURES

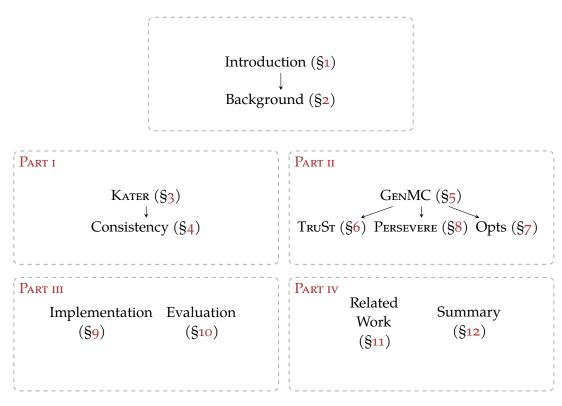

| 1.1  | The part- and chapter dependencies of the thesis                      | 4   |

|------|-----------------------------------------------------------------------|-----|

| 2.1  | <b>MP</b> : three consistent execution graphs under SC                | 12  |

| 3.1  | A counterexample produced by KATER                                    | 35  |

| 4.1  | Consistency checks with KATER <sup>1</sup>                            | 39  |

| 4.2  | An inconsistent execution under SC                                    | 39  |

| 4.3  | Writes-before relation: Two cases of induced edges .                  | 42  |

| 5.1  | w+w+R: interleavings and equivalences classes                         | 50  |

| 5.2  | The graphs of $w+w+R$ subsume its equivalence classes                 | 50  |

| 5.3  | LB+DEP: $x = y = v$                                                   | 50  |

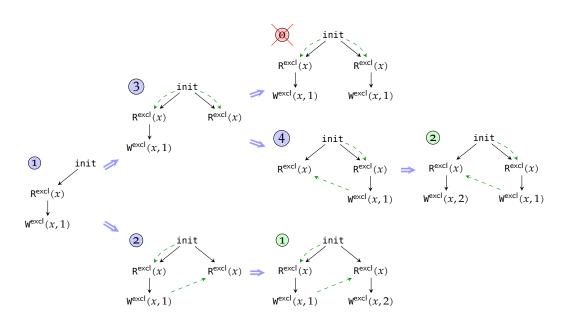

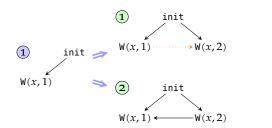

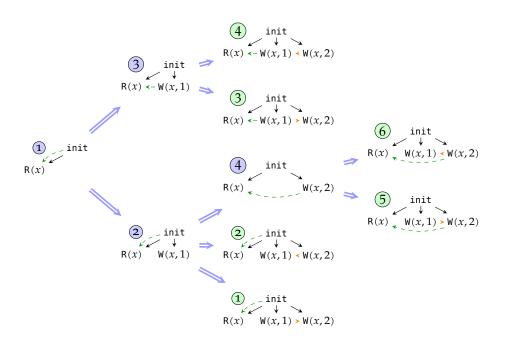

| 5.4  | Execution graphs of w+rw+w under SC                                   | 52  |

| 5.5  | GENMC: Enumerating the execution graphs of w+RW+W                     | 53  |

| 5.6  | A prefix-closed execution of <b>LB-EXT</b> under POWER                | 56  |

| 5.7  | A prefix-closed execution of <b>MP-EXT</b> under POWER .              | 56  |

| 5.8  | The executions of the FAI/2 program                                   | 57  |

| 5.9  | GENMC: Enumerating the execution graphs of FAI/2.                     | 58  |

| 5.10 | Execution graphs of $w+Rw+w$ under SC (with co).                      | 59  |

| 5.11 | GENMC: Enumerating co-tracking graphs of w+w                          | 60  |

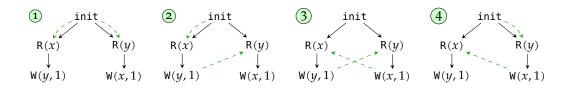

| 5.12 | Execution graphs of LB                                                | 61  |

| 5.13 | GENMC: Enumerating the execution graphs of LB                         | 61  |

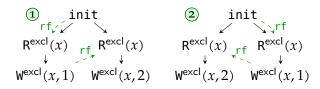

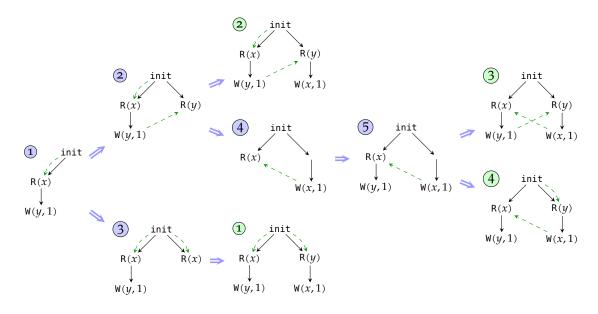

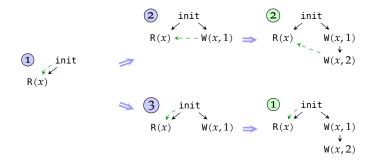

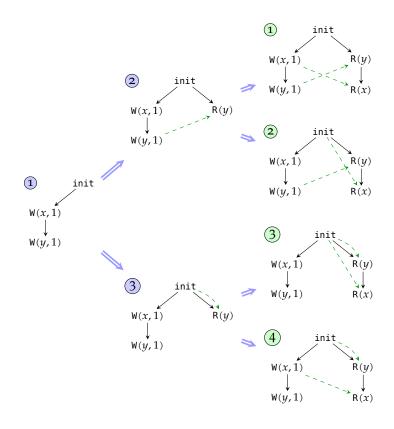

| 6.1  | TRUST: Enumerating the execution graphs of RR+w+w                     | 69  |

| 6.2  | TRUST: Enumerating the execution graphs of $R+w+w$                    | 70  |

| 6.3  | Revisiting a read multiple times is often necessary .                 | 71  |

| 7.1  | A toy implementation of synchronization barriers                      | 81  |

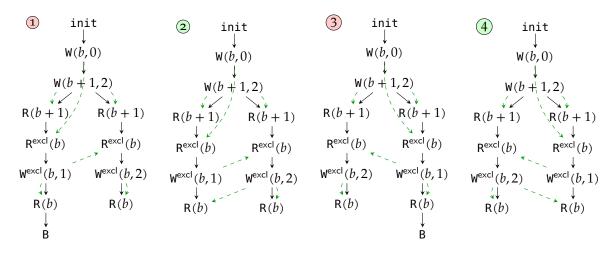

| 7.2  | Execution graphs of <b>BARRIER-</b> <i>N</i> for $N = 2$              | 82  |

| 7.3  | Unordered barriers: a single graph for $\frac{\text{BARRIER-}N}{N}$ . | 83  |

| 7.4  | An invalid graph for BARRIER-N-SYNC                                   | 84  |

| 7.5  | BAM: Execution graph of BARRIER-N-SYNC for $N = 2$ .                  | 84  |

| 7.6  | An invalid sbr relation for BARRIER2- $N$                             | 84  |

| 7.7  | CFGs for the two threads of LOOP-PEEL.                                | 89  |

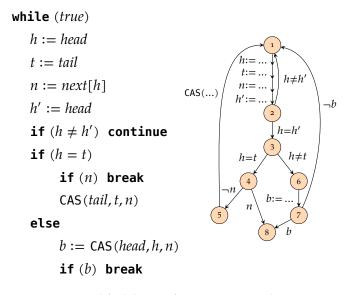

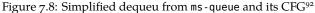

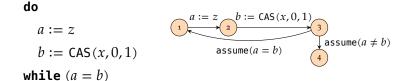

| 7.8  | Simplified dequeu from $ms$ -queue and its $CFG^1$                    | 90  |

| 7.9  | Example where static purity inference is impossible .                 | 93  |

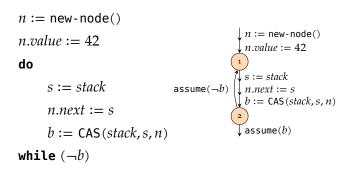

| 7.10 | Simplified push from treiber-stack and its $\ensuremath{CFG}^1$ .     | 93  |

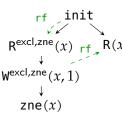

| 7.11 | Graph encountered during the exploration of ZNE-OBS.                  | 96  |

| 7.12 | Freezing writes example                                               | 02  |

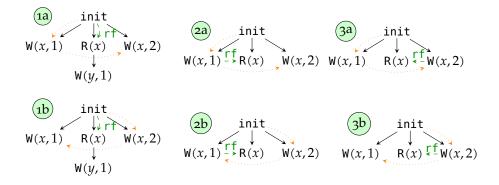

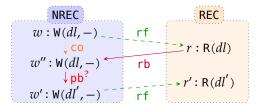

| 8.1  | An instrumented execution precluded by <b>REC</b> 1                   | 109 |

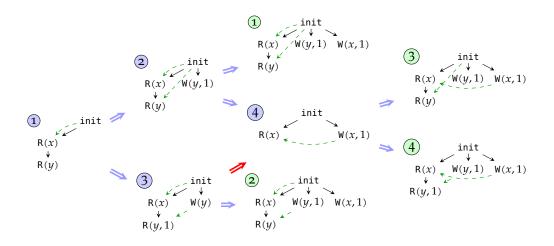

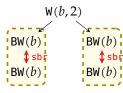

| 8.2  | Persevere: Enumerating post-crash states of <b>REC-WW+RR</b>          | 111 |

| 9.1  | GenMC's overall architecture                                          | 117 |

| 9.2  | The "SSA-CFG" of thread II of LOOP-PEEL 1                             | 20  |

| 9.3  | Merging bisimilar nodes in SSA 1                                      | 20  |

| 9.4  | GenMC's verification components                                       | 22  |

| 9.5  | A liveness violation for w+r-loop                                     | 125 |

| 9.6  | GenMC error report after removing irrelevant lines . 126                |

|------|-------------------------------------------------------------------------|

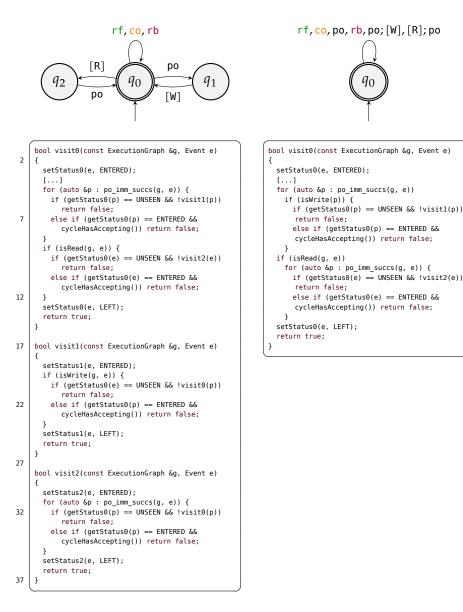

| 9.7  | KATER-generated code for SC-consistency checking . 127                  |

| 9.8  | NFA <sub>TSO</sub> before and after merging predicate transitions $128$ |

| 9.9  | The psc acyclicity axiom of RC11 in kat 129                             |

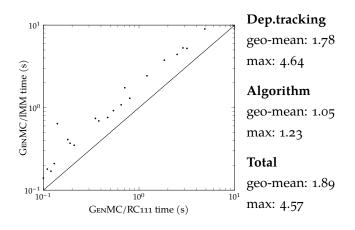

| 10.1 | Overhead of dependency tracking                                         |

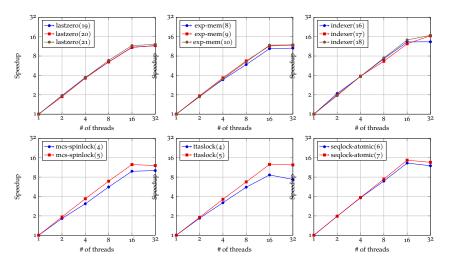

| 10.2 | GenMC scalability on 16 physical (32 logical) cores . $\  \  152$       |

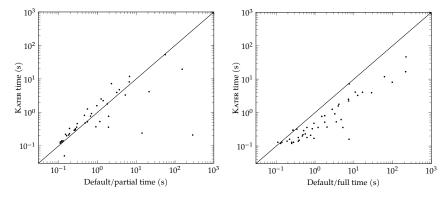

| 10.3 | Default vs kater-generated consistency checks 154                       |

| 11.1 | A partial order of proposed equivalence partitionings 162               |

## LIST OF TABLES

| 10.1  | Proving correctness of queries with KATER           | 132 |

|-------|-----------------------------------------------------|-----|

| 10.2  | Synthetic benchmarks with only loads and stores     | 136 |

| 10.3  | Synthetic benchmarks taken from SV-COMP [SV-19]     | 137 |

| 10.4  | Synthetic benchmarks with RMW instructions          | 138 |

| 10.5  | Benchmarks adapted from Pulte et al. [Pul+19]       | 139 |

| 10.6  | Benchmarks adapted from Norris and Demsky [ND13]    | 140 |

| 10.7  | Synthetic benchmarks (24h timeout)                  | 142 |

| 10.8  | Weak memory benchmarks (24h timeout)                | 143 |

| 10.9  | Synthetic benchmarks with only barrier operations . | 145 |

| 10.10 | Benchmarks with realistic barrier use cases         | 146 |

| 10.11 | Real-world benchmarks                               | 147 |

| 10.12 | Benefits of bisimilarity                            | 149 |

| 10.13 | Benefits of blocking prevention                     | 150 |

| 10.14 | SC benchmarks                                       | 155 |

| 11.1  | An overview of the bounded verification landscape . | 167 |

# LIST OF ALGORITHMS

| 2.1 | Check that $G$ is an execution of program $P$     | 13 |

|-----|---------------------------------------------------|----|

| 2.2 | Check that $G$ is an execution of program $P$     | 16 |

| 4.1 | KATER: Checking consistency in linear time        | 44 |

| 4.2 | Fixpoint for approximating <b>co</b> in a model M | 45 |

| 5.1 | Generating events incrementally                   | 63 |

| 5.2 | Choosing non-blocked threads                      | 63 |

| 5.3 | GenMC: Generic Model Checking                     | 65 |

| 6.1 | TRUST: Backward-revisiting condition              | 72 |

| 6.2 | TruST: Iterative version with linear memory         | 73 |

|-----|-----------------------------------------------------|----|

| 6.3 | TruSt: Iterative version (backtracking)             | 75 |

| 6.4 | Prev: Backward step from G to $G_p$                 | 76 |

| 7.1 | Adaptation of NextEvent for BAM                     | 85 |

| 7.2 | Adaptation of algorithm 5.3 for BAM 8               | 86 |

| 7.3 | ZNE Spinloop Validity Check                         | 96 |

| 7.4 | Adaptation of NextEvent for SAVer                   | 97 |

| 7.5 | Calculate the blocking condition at a given node 10 | 00 |

| 7.6 | Preventing blocking in DPOR                         | 53 |

|     |                                                     |    |

### ACRONYMS

| CAS  | :   | Compare-and-Swap                |

|------|-----|---------------------------------|

| CFG  | :   | Control-Flow Graph              |

| DFS  | :   | Depth-first Search              |

| DPOF | R : | Dynamic Partial Order Reduction |

| FAI  | :   | Fetch-and-Increment             |

| RA   | :   | Release-Acquire                 |

| SC   | :   | Sequential Consistency          |

| SCC  | :   | Strongly Connected Component    |

| SMC  | :   | Stateless Model Checking        |

| SSA  | :   | Static Single Assignment        |

| TSO  | :   | Total Store Ordering            |

|      |     |                                 |

In the modern age of computing, the world is concurrent: from multicore CPUs all the way up to the network stack and the users themselves, operations take place concurrently. In turn, reasoning about concurrency is of utmost importance.

This thesis focuses on *automated reasoning* of concurrent programs.

Traditionally, automated reasoning techniques assume sequential consistency  $(SC)^1$ , i.e., that all the behaviors of a concurrent program can be generated by some arbitrary interleaving of its threads. This assumption, however, is wrong. Due to compiler and/or hardware optimizations, concurrent programs can exhibit a number of additional behaviors, which are referred to as "weak" behaviors.

As an example, consider the **MP** program below, where *data* and *flag* are shared variables (initially 0), and || separates different threads:

$$\begin{array}{c|c} data := 42 \\ flag := 1 \end{array} & \begin{array}{c} \text{if } (flag = 1) \\ \text{assert}(data = 42) \end{array} \end{array}$$

Under SC, this program is safe: if thread II reads flag = 1, the write to *data* will already have happened, and the assertion will not be violated. In architectures like ARMv8 or POWER<sup>2</sup>, however, the CPU is within its rights to *reorder* the instructions of thread I, thereby leading to a weak behavior where thread II reads flag = 1 and data = 0.

Reasoning about concurrency in the presence of such behaviors requires precise models. The formal models describing the exact behaviors that concurrent programs can exhibit are called (*weak*) *memory models*, while the field that studies such models is called *weak memory consistency* (or simply weak memory).

In the past few years, a plethora of memory models has emerged. These models do not solely concern hardware architectures like ARMv8 and POWER, but also extend to languages like C/C++ and Java<sup>3</sup>. Indeed, the purpose of such language models is not merely to define the behaviors of the CPU, but rather to define the concurrency semantics at the level of the programming language, and provide guarantees that carry over all the way down to the produced binary.

#### 1.1 CHALLENGES OF WEAK MEMORY CONSISTENCY

Along with the emergence of weak memory models, new challenges to automated reasoning emerged. This thesis addresses two major challenges. <sup>1</sup> "How to Make a Multiprocessor Computer that Correctly Executes Multiprocess Programs" [Lam79]

<sup>2</sup> "Herding cats: Modelling, simulation, testing, and data mining for weak memory" [AMT14]

<sup>3</sup> "Mathematizing C++ concurrency" [Bat+11]; "The Java memory model" [MPA 05] First, how do we establish that a given memory model M satisfies its intended metatheoretic properties? A concrete example of such a property would be the correctness of a local program transformation in M (e.g., reordering of independent memory accesses). For such a transformation to be sound in M, it must not introduce any new behaviors.

Unfortunately, even though there is a long line of work trying to establish such properties for various memory models, these topics used to require lengthy human investigation, and were extremely error prone: most proposed language models were initially broken (e.g., C/C++, Java) and required multiple iterations to achieve soundness.

Second, how do we verify programs under weak memory consistency? As we are interested in automated verification, *model checking*<sup>4</sup> seems like the obvious solution. In a nutshell, model checking verifies a program (expressed as a finite-state machine) by exploring all its reachable states, and checking that none of them violates a provided specification.

Despite its success in the context of sequential programs, model checking is inadequate when it comes to concurrency. A first major disadvantage is the increased memory consumption caused by the stateexplosion problem. Indeed, as the state space of a concurrent program grows larger, so does the memory required to keep track of all explored states, rendering verification intractable. A second (and perhaps more relevant) limitation is that model checking does not gracefully extend to weak memory models. Even though the effects of certain weak memory models can be simulated by encoding instruction reorderings as non-deterministic choice, such an encoding further blows up the state space, leaving much to be desired for concurrent program verification.

#### 1.2 CONTRIBUTIONS

This thesis presents scalable and practical solutions to both challenges arising from weak memory models.

First, it presents KATER, a sound, complete, and automated way to prove metatheoretic properties of weak memory models. More specifically, the thesis shows that most metatheoretic queries can be solved by answering a more fundamental question: "Given two memory models, is one weaker than the other?" For a wide class of weak memory models, this basic question can be reduced to a language inclusion problem between regular languages, which is decidable. KATER can answer metatheoretic queries in a matter of seconds, effectively sparing years of manual proof efforts.

Second, it presents GENMC, a model-checking algorithm that is *parametric* in the choice of the memory model, and has *linear* memory consumption in the size of the program under test. GENMC is a based on a technique called *dynamic partial order reduction* (DPOR)<sup>5</sup>, which, under

<sup>4</sup> "Automatic verification of finite-state

concurrent systems

Using temporal

logics specification: A practical

approach" [CES83]

<sup>5</sup> "Dynamic partial-order reduction for model checking software" [FG05] SC, verifies a concurrent program by partitioning its interleavings into equivalence classes, and then striving to explore one interleaving per equivalence class.

Crucially, GENMC reconciles two notions that were incompatible in past DPOR approaches: linear memory consumption and optimality (i.e., exploring one interleaving per equivalence class). Prior techniques would either require memory exponential in the size of the program under verification, or explore (exponentially) many unnecessary interleavings. By contrast, GENMC is the first DPOR framework that is a) optimal, b) has linear memory consumption, and c) is memory-model-parametric.

Finally, in addition to a number of optimizations that enhance its performance for various programming patterns such as synchronization barriers, locks and spinloops, GENMC extends DPOR for *persistency models* as well. Similarly to how weak memory models describe the behaviors that concurrent programs can exhibit (i.e., the values that their loads can read), persistency models describe the behaviors that persistent storage (e.g., hard drive, non-volatile memory) can exhibit in the presence of crashes. GENMC is the first DPOR algorithm that can verify persistency properties of both sequential and concurrent programs.

A key ingredient of both solutions above was a shift in representation. Rather than following existing work and representing program executions as traces, this thesis employs *declarative semantics*<sup>6</sup> and represents executions as partially-ordered structures known as *execution graphs*. Execution graphs are used in the weak memory literature to formalize the concurrency semantics of modern hardware architectures.

Using declarative semantics is crucial for both contributions. For KATER, declarative semantics is key in observing that most weak memory models can be expressed using Kleene Algebra with Tests (KAT)<sup>7</sup>, an observation that largely explains why metatheoretic queries can be automated. In the case of GENMC, execution graphs not only subsume the equivalence classes that are used by traditional DPOR approaches, but also enable support for weak memory consistency. In other words, execution graphs form a new foundation for DPOR, suitable for model checking under weak memory.

#### 1.3 STRUCTURE

The thesis is structured in four parts.

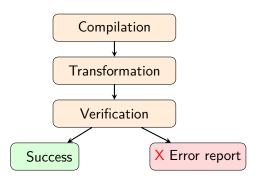

**PART I** deals with weak memory metatheory. First, it describes how KATER automates weak memory metatheory (§3), and then how consistency is checked in execution graphs, and how KATER can be used to synthesize code that checks whether a given graph is consistent (§4).

**PART II** describes GENMC. After a brief introduction to DPOR, it describes the basic algorithm of GENMC and the requirements it sets on the underlying weak memory model (§5), and then how the algorithm

<sup>6</sup> "Herding cats: Modelling, simulation, testing, and data mining for weak memory" [AMT14]

<sup>7</sup> "Kleene Algebra with Tests" [Koz97]

Figure 1.1: The part- and chapter dependencies of the thesis.

is modified in order to achieve linear memory consumption (§6). Subsequently, we explain how GENMC can be extended to handle persistency models (§8), and the optimizations that enhance its scalability in the presence of various programming patterns (§7).

PART III describes the implementation of KATER and GENMC ( $\S$ 9), and evaluates the tools on various benchmarks ( $\S$ 10).

**PART IV** concludes with a description of related work (§11), a summary of the contributions, and some future directions (§12).

These four parts are split in three layers (see Fig. 1.1). Each layer assumes knowledge of the layer above it, but not of the parts on the same layer or the layers below. Analogously, a chapter in a given part only depends on the chapters above it. Each chapter begins with a high-level description of the problem being solved, the key idea underpinning the solution, and a chapter outline.

Throughout the thesis, non-colored hyperlinks are used to connect definitions to their usages. Such hyperlinks are used for the employed notation (e.g., sbr), terms (e.g., maximal extension), as well as for certain exploration examples (e.g., 2). In certain viewers (e.g., skim in MacOS, evince in GNU/Linux), hovering over such hyperlinks offers a preview of the target.

#### 1.4 PUBLICATIONS AND IMPACT

**PUBLICATIONS** The work making up this thesis has been published in the following papers (in reverse chronological order):

POPL 2023 KATER: Automating Weak Memory Metatheory and Consistency Checking Michalis Kokologiannakis, Ori Lahav, Viktor Vafeiadis [KLV23b]

POPL 2022 Truly Stateless, Optimal Dynamic Partial Order Reduction Michalis Kokologiannakis, Iason Marmanis, Vladimir Gladstein, Viktor Vafeiadis [Kok+22a]

FMCAD 2021 Dynamic Partial Order Reductions for Spinloops Michalis Kokologiannakis, Xiaowei Ren, Viktor Vafeiadis [KRV21]

CAV 2021 GENMC: A Model Checker for Weak Memory Models Michalis Kokologiannakis, Viktor Vafeiadis [KV21b]

NETYS 2021 BAM: Efficient Model Checking for Barriers Michalis Kokologiannakis, Viktor Vafeiadis [KV21a]

POPL 2021 PerSeVerE: Persistency Semantics for Verification under Ext4

Michalis Kokologiannakis, Ilya Kaysin, Azalea Raad, Viktor Vafeiadis [Kok+21]

ASPLOS 2020 HMC: Model Checking for Hardware Memory Models Michalis Kokologiannakis, Viktor Vafeiadis [KV20]

PLDI 2019 Model Checking for Weakly Consistent Libraries Michalis Kokologiannakis, Azalea Raad, Viktor Vafeiadis [KRV19]

TOOLS GENMC and KATER are provided as open-source tools. The following repositories contain instructions on how to build and use the tools:

- KATER: https://github.com/MPI-SWS/kater

- GENMC: https://github.com/MPI-SWS/genmc

Among the two tools, GENMC has been more successful (perhaps due to it being more mature) and has attracted some industrial users. As an example, Huawei researchers have used it to verify and optimize the placement of fences in their synchronization library <sup>8</sup>, while other works have found bugs in published algorithms <sup>9</sup> and in Microsoft's mimalloc allocator <sup>10</sup>.

While working on extending GENMC for persistency models, we also used GENMC to reproduce a bug in the nano text editor, and formally verify our fix<sup>11</sup>.

<sup>8</sup> "VSync: Push-Button Verification and Optimization for Synchronization Primitives on Weak Memory Models" [Obe+21b]

<sup>9</sup> "Verifying and Optimizing the HMCS Lock for Arm Servers" [Obe+21a]

<sup>10</sup> Play nice with thread sanitizer #130 [*mar*]; fix memory order for weak CAS [*daa*]

<sup>11</sup> "PerSeVerE: Persistency semantics for verification under ext4" [Kok+21]

#### 6 INTRODUCTION

SUPPLEMENTARY MATERIAL All papers and supplementary material making up this thesis (including proofs and Coq development, where available) can be found at the following pages:

- KATER: https://plv.mpi-sws.org/kater

- GENMC: https://plv.mpi-sws.org/genmc

- GENMC for persistency models: https://plv.mpi-sws.org/persevere

- Benchmarks and tools (§10): doi.org/10.5281/zenodo.10575926

#### BACKGROUND

Following the standard declarative (a.k.a. axiomatic) approach of weak memory models, the semantics of a given program is given as a set of allowed outcomes. These outcomes are expressed as *execution graphs*<sup>12</sup>.

In this chapter, we present how programs are mapped to execution graphs. First, we define a toy programming language ( $\S$ 2.1), then, we define execution graphs ( $\S$ 2.2) and demonstrate how they are used in declarative semantics ( $\S$ 2.3), and finally, we show how execution graphs are constructed from programs ( $\S$ 2.4).

RELATIONAL NOTATION We write  $\emptyset$ , univ, and id for the empty, the full, and the identity relation, respectively. Given a relation r, we write  $r^{-1}$  for its inverse (i.e.,  $\{\langle a, b \rangle \mid \langle b, a \rangle \in r\}$ ), and  $r^{?}$ ,  $r^{+}$  and  $r^{*}$  for its reflexive, transitive and reflexive-transitive closures, respectively. We write dom(r) and rng(r) for the domain and range of r, respectively, and  $r|_{imm}$  for the immediate edges in r, i.e.,  $r \setminus (r; r)$ . Given a set *S*, we write  $r|_{S}$  for the restriction of r on *S*. Given two relations  $r_{1}$  and  $r_{2}$ , we write  $r_{1}$ ;  $r_{2}$  for their relational composition, i.e.,  $\{\langle a, b \rangle \mid \exists c. \langle a, c \rangle \in r_{1} \land \langle c, b \rangle \in r_{2}\}$ . Given a set *A*, we write [*A*] for the identity relation on *A*:  $\{\langle a, a \rangle \mid a \in A\}$ .

We say that a relation r is *irreflexive* if  $\nexists a. \langle a, a \rangle \in r$  and *acyclic* if  $r^+$  is irreflexive. A relation is a *strict partial order* if it is irreflexive and transitive. A relation r is *total* on a set A if  $\langle a, b \rangle \in r \cup r^{-1} \cup [A]$  for all  $a, b \in A$ . A relation is a *strict total order* on a set A if it is a strict partial order that is total on A.

Given a total order r on a set A and an element  $a \in A$ , we write  $succ_r(a)/pred_r(a)$  for the immediate successor/predecessor of a in r. Given a set  $S \subseteq A$ , we write  $max_r(S)/min_r(S)$  for the r-maximal/minimal element in S.

#### 2.1 PROGRAMMING LANGUAGE

We start by defining a simple untyped assembly language. Instructions in our language,  $i \in Inst$ , are given by the following grammar:

$$i ::= r := e \mid r := [e]^{a_{\mathsf{R}}} \mid [e_1]^{a_{\mathsf{W}}} := e_2 \mid \mathsf{fence}^{a_{\mathsf{F}}} \mid \mathsf{if} \ e \ \mathsf{goto} \ n$$

where  $r \in \text{Reg}$  ranges over registers,  $n \in \mathbb{N}$  over integers, and  $e \in \text{Exp}$  over simple expressions built from integers, registers, and arithmetic operators:

$$e ::= n | r | e_1 + e_2 | e_1 - e_2 | \dots$$

<sup>12</sup> "Herding cats: Modelling, simulation, testing, and data mining for weak memory" [AMT14] <sup>13</sup> The precise definition of access modes is not important for this thesis and depends on the memory model. For example, C11 [Bat+11] has non-atomic, relaxed, acquire, release, and SC accesses. In the instructions above,  $a_R \subseteq \text{Rattr}$ ,  $a_W \subseteq \text{Wattr}$ , and  $a_F \subseteq \text{Fattr}$  range over read, write, and fence *attributes*, respectively, many of which are going to be introduced in subsequent chapters. Attributes include the mode of a memory access<sup>13</sup>, which can be used to enforce synchronization, as well as the exclusivity flag, excl, denoting whether a memory access is part of an atomic read-modify-write (RMW) instruction (see below).

Returning to the instructions, r := e assigns the value of e to register r (without any effect on memory); r := [e] reads the value in the address pointed by e and stores it in register r;  $[e_1] := e_2$  stores the value contained in  $e_2$  in the address contained in  $e_1$ ; fence<sup> $a_f$ </sup> is used to place global barriers; and **if** e **goto** n jumps to n if e has a non-zero value. We assume that the special addresses block and error denote program blocking and error, respectively.

Notice that our language does not contains atomic read-modify-write (RMW) operations or functions like assert and assume, as these can be defined as syntactic sugar over a sequence of instructions:

```

r := \mathsf{CAS}(e_1, e_2, e_3) \triangleq r := [e_1]^{\mathsf{excl}}

\mathbf{if} \ r \neq e_2 \ \mathbf{goto} \ pc + 2

[e_1]^{\mathsf{excl}} := e_3

r := \mathsf{fetch}_\mathsf{add}(e_1, e_2) \triangleq r := [e_1]^{\mathsf{excl}}

[e_1]^{\mathsf{excl}} := e_2 + r

\mathsf{assert}(e) \triangleq \mathbf{if} \neg e \ \mathbf{goto} \ \mathsf{error}

\mathsf{assume}(e) \triangleq \mathbf{if} \neg e \ \mathbf{goto} \ \mathsf{block}

```

where  $pc \in \text{Reg}$  is the program counter.

Finally, a sequential program, *S*, is simply a collection of instructions (defined as a finite map from  $\mathbb{N}$  to instructions), while a concurrent program, *P*, is a parallel composition of sequential programs (defined as a finite map from thread identifiers to sequential programs).

In all examples, we use vertical alignment to denote sequences of instructions and || for the parallel composition of threads. We use x, y, z for global (shared) variables and a, b, c, ... for registers. We also omit the square brackets for global variables, as their address is known and does not need to be computed (as in e.g., the MP example of §1).

**Remark 1.** The actual implementation of GENMC does not operate on the toy language defined above. It operates on the level of LLVM-IR, and can handle the full complexity of languages like C and C++ (including dynamic thread creation, parts of the standard library, etc). As such features are orthogonal to the weak memory semantics, we omit them here. See §9.2 for more details.

#### 2.2 EXECUTION GRAPHS

An execution graph *G* models a distinct behavior of a given program. It comprises (a) a set of events (nodes), modeling instructions of the program, and (b) some relations on these events (edges), modeling the various interactions between the instructions. The two kinds of relations present in all memory models are the *program order* (po), ordering events in a given thread, and the *reads-from* relation (rf), which relates each read event *r* in *G* to a write event *w* in *G*, from which *r* obtains its value.

Let us begin by defining execution graph events.

**Definition 2.2.1.** An *event*,  $e \in Event$ , is either the initialization event init, or a thread event  $\langle t, n, lab \rangle$  where  $t \in Tid$  is a thread identifier,  $n \in Idx \triangleq \mathbb{N}$  is a serial number inside each thread, and  $lab \in Lab$  is a label that takes one of the following forms:

- Read label:  $\mathbb{R}^{a_{\mathbb{R}}}(l)$  where  $a_{\mathbb{R}} \subseteq \mathbb{R}$  attr denotes any attributes the read might have, and  $l \in \text{Loc}$  is the location accessed.

- Write label: W<sup>a</sup><sub>W</sub>(l, v) where a<sub>W</sub> ⊆ Wattr denotes any attributes the write might have, l ∈ Loc is the location accessed, and v ∈ Val the value written.

- Fence label: F<sup>a<sub>F</sub></sup> where a<sub>F</sub> ⊆ Fattr denotes any attributes the fence might have.

- Block label: B denotes the blockage of a thread (due to reaching the block address).

- Error label: Error denotes a thread error (due to reaching the error address).

Given an event *e*, we use *e*.tid, *e*.idx and *e*.lab to project to its components. We omit the  $\emptyset$  for read/write labels with no attributes. The functions tid, idx, and loc, respectively return the thread identifier, serial number, and location of an event, when applicable. We use R, W, B, and error to denote the set of all read, write, block, and error events, respectively, and assume that init  $\in$  W. We use superscript and subscripts to further restrict those sets (e.g.,  $W_l \triangleq {\text{init}} \cup {w \in W | \text{loc}(w) = l}$ ).

Observe that event labels correspond to instructions with memory side-effects. Assignments (r := e) and conditionals (**if** e **goto** n) do not generate any events.

Now, we can formally define execution graphs as follows.

**Definition 2.2.2.** An *execution graph*  $G \in Exec$  consists of:

- 1. a sequence G.E of distinct events, and

- 2. the reads-from relation  $G.rf \subseteq W \times R$ , that relates each write event to the same-location reads that read from it.

We often use *G*.E to denote the set of graph events (implicit conversion). We write *G*.R for the set *G*.E  $\cap$ R and similarly for other sets. Given two events  $e_1, e_2 \in G$ .E, we write  $e_1 <_G e_2$  if  $e_1$  precedes  $e_2$  in *G*.E, and  $e_1 \leq_G e_2$  if  $e_1 <_G e_2$  or  $e_1 = e_2$ . We write  $G|_E$  for the restriction of an execution graph *G* to a set of events *E*, and  $G \setminus E$  for the graph obtained by removing a set of events *E*. Finally, we write  $G_1 \approx G_2$  if the  $G_1$ .E is a permutation of  $G_2$ .E, and  $G_1$  and  $G_2$  agree on all other components.

Observe that the definition of graphs does not contain a *program order* (po) as an explicit component, since *G*.po can be recovered from the representation of events: it relates the initialization event before all other events, and events in the same thread according to their *n* component.

$$G.\mathsf{po} \triangleq \{ \langle \mathsf{init}, e \rangle \mid e \in G.\mathsf{E} \setminus \{\mathsf{init}\} \} \cup \\ \{ \langle e, e' \rangle \in G.\mathsf{E} \times G.\mathsf{E} \mid \mathsf{tid}(e) = \mathsf{tid}(e') \land \mathsf{idx}(e) < \mathsf{idx}(e') \}$$

We write  $G.rmw = [G.R^{excl}]; G.pol_{imm}; [G.W^{excl}]$  for the restriction of po to (immediate) pairs forming RMW instructions<sup>14</sup>.

As far as the rf relation is concerned, we ensure that it only relates same-location events by requiring that *G* be well-formed:

**Definition 2.2.3** (Well-formedness). An execution graph *G* is *well-formed* if the following hold for *G*.rf:

- 1. *G*.rf only relates writes and reads with matching locations, i.e., for every  $\langle w, r \rangle \in G$ .rf it is  $w \in G.W$ ,  $r \in G.R$ , loc(w) = loc(r),

- 2. *G*.rf is functional on its range, i.e., if  $\langle w_1, r \rangle$ ,  $\langle w_2, r \rangle \in G$ .rf it is  $w_1 = w_2$ , and

- 3. each read reads a value, i.e.,  $\forall r \in G.R. \exists w. \langle w, r \rangle \in G.rf.$

As rf is functional on its range, we sometimes write G.rf(r), to refer to the unique write  $w \in G.W$  such that  $\langle w, r \rangle \in G.rf$ , and write G.val(e)for the value read/written by a read/write.

We write *G*.porf for  $(G.po \cup G.rf)^+$ , and also define the *causal order* of a graph, and the *causal prefix* of an event *e* as follows:

$G.\mathsf{corder} \triangleq G.\mathsf{porf}$  $G.\mathsf{cprefix}(e) \triangleq \{e' \in G.\mathsf{E} \mid \langle e', e \rangle \in G.\mathsf{corder}\}$

Intuitively, the causal prefix of an event *e* represents the minimal set of events that need to be executed before executing *e*.

The *same-location* relation, sameloc, relates pairs of events that have the same location: sameloc  $\triangleq \{\langle e_1, e_2 \rangle \in \text{Event} \times \text{Event} | \text{loc}(e_1) = \text{loc}(e_2) \}$ . Using sameloc, we define a per-location version of po as poloc  $\triangleq \text{po} \cap$  sameloc.

Finally, most memory models also make use of the *coherence order* relation, **co**, which totally orders the writes in each memory location. As such, we define the following augmented version of execution graphs.

<sup>14</sup> For executions coming from programs (see §2.4), for every  $\langle r, w \rangle \in G.rmw$ , it always is loc(r) = loc(w). **Definition 2.2.4.** A *coherence-tracking execution graph G* is an execution graph with the following extra relation:

1. the *coherence order*,  $G.co \subseteq \bigcup_{l \in Loc} G.W_l \times G.W_l$ , a strict partial order which is total on  $G.W_l$  for every location  $l \in Loc$ .

In what follows, we write execution graph, graph, or execution to denote either a plain or a coherence-tracking execution graph. We explicitly disambiguate when necessary.

#### 2.3 WEAK MEMORY CONSISTENCY MODELS

In declarative semantics, a memory model M is expressed using a consistency predicate,  $consistent_M(\cdot)$ , denoting what kind of behaviors are allowed under M. In turn, the semantics of a program *P* under M is given by the set of (well-formed) execution graphs corresponding to the program that satisfy the consistency predicate of M (see §2.4).

Consistency predicates generally constrain the possible choices of co and rf, which indirectly constrain the possible final values of memory locations and the values that reads can return. A non-coherence-tracking execution graph is consistent if there exists some co such that the resulting coherence-tracking execution graph is consistent.

For instance, SC<sup>15</sup> can be defined by making use of two auxiliary definitions.

First, we define the *reads-before* (a.k.a. from-read) relation to relate a read *r* and a write *w* if *r* reads from a co-earlier write than *w*:  $rb \triangleq G.rf^{-1}$ ; co.

Then, we define RMW-atomicity to disallow two RMWs to read from the same write:

**Definition 2.3.1** (RMW-atomicity). An execution graph *G* is *RMW-atomic* iff there are no two distinct exclusive reads that have corresponding exclusive writes (i.e.,  $r_i \in dom(G.rmw)$  for  $i \in \{1, 2\}$ ) and read from the same write w (i.e.,  $\langle w, r_i \rangle \in G.rf$  for  $i \in \{1, 2\}$ ).

**Definition 2.3.2** (SC). An execution graph *G* is *sequentially consistent*, written consistent<sub>SC</sub>(*G*), iff *G* is RMW-atomic and  $(G.porf \cup G.co \cup rb)^+$  is irreflexive.

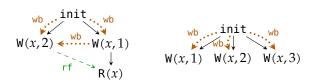

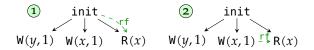

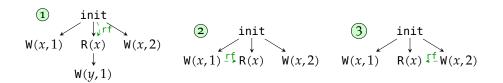

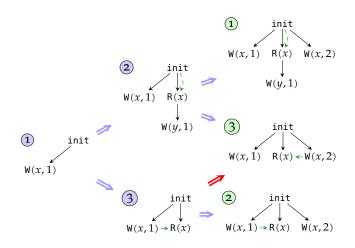

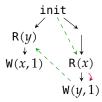

As a concrete example of how consistency predicates rule out inconsistent executions, consider the MP program from §1 and its three consistent executions<sup>16</sup> under SC in Fig. 2.1. Intuitively, the MP program has three consistent executions under SC, because SC forbids the load of *data* to read from the initial state as the load is already aware of the flag := 1 store. Formally, reading flag = 1 and data = 0 creates an SCcycle due to the rb edge from R(*data*) to W(*data*, 42)<sup>17</sup>. Other models such as the "relaxed" fragment of RC11<sup>18</sup> allow this behavior. <sup>15</sup> "How to Make a Multiprocessor Computer that Correctly Executes Multiprocess Programs" [Lam79]

<sup>16</sup> Throughout this thesis, we use greencircled numbers for consistent executions, and red-circled numbers for inconsistent ones. <sup>17</sup> We generally do not depict co and rb edges to avoid cluttering the presentation 18 "Repairing sequential consistency in C/C++11" [Lah+17]

Figure 2.1: MP: three consistent execution graphs under SC.

<sup>19</sup> For SC, hb can be defined as hb ≜ (porf ∪ co ∪ rb)<sup>+</sup>, as all instructions imply synchronization. Certain models enforce synchronization via a *happens-before* relation, hb  $\supseteq$  po, prescribing the order induced by synchronization mechanisms, e.g., locks<sup>19</sup>. Even though we do not restrict our framework to an explicit memory model, some of the algorithms presented later on (e.g., §7.1), do rely on the existence of hb. For these algorithms, we assume that hb is a parameter of the memory model, with the proviso that for all executions  $G \in \text{Exec}$ , if consistent<sub>M</sub>(*G*) holds, then hb is a strict partial order.

Finally, models often define certain graphs as erroneous (e.g., due to data races). To account for this, we also assume an error predicate,  $IsErroneous_{M}(\cdot)$ , denoting whether a given (consistent) graph is erroneous, and require it to be monotone: for all *G* and  $E \subseteq G.E$ , if  $dom(G.corder; [E]) \subseteq E$  and  $IsErroneous_{M}(G|_{E})$ , then  $IsErroneous_{M}(G)$ . We call a graph *G* M-erroneous if  $IsErroneous_{M}(G)$  holds.

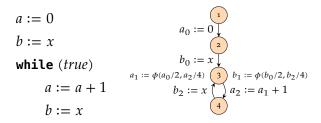

#### 2.4 FROM PROGRAMS TO EXECUTION GRAPHS

Now that we have defined execution graphs and consistency under weak memory, let us see how programs are mapped to sets of consistent execution graphs. We do so by defining the  $E_{XEC}P_{ROGRAM}(P,G)$  procedure (algorithm 2.1), which checks that the execution *G* corresponds to some run of the program *P*. Later, in §5.8, we extend this procedure to also generate the execution incrementally.

EXECPROGRAM interprets the program P and checks that the memory accesses generated match those recorded in G. After all threads have been interpreted, EXECPROGRAM ensures that G does not contain events from threads not originating from P (line 4).

The interpretation of each thread is performed by EXECTHREAD. For each thread *t* of the program (line 2), EXECTHREAD constructs a configuration of the form  $\langle t, n, \Phi \rangle$ , where *n* is the index in *t* that was considered, and  $\Phi : \text{Reg} \rightarrow \text{Val}$  is the *register file* that maps registers to values. Initially, *n* is set to 0 signaling that no events have yet been checked for *t*, and every register has the value 0 (line 6).

The register set includes a special register, the *program counter* (pc), that points to the next instruction to be executed. The program counter is incremented by every instruction (line 8), except for conditional

```

Algorithm 2.1 Check that G is an execution of program P

1: procedure ExecProgram(P, G)

for \langle t, sprog \rangle \in P do

2:

ExecThread(t, sprog, G)

3:

assert(\forall e \in G.E. P(tid(e)) \neq \bot)

4:

procedure ExecTHREAD(t, sprog, G)

5:

\langle t, n, \Phi \rangle \leftarrow \langle t, 0, \lambda r, 0 \rangle

6:

while i \leftarrow sprog(\Phi(pc)) do

7:

\Phi(pc) \leftarrow \Phi(pc) + 1

8:

ExecInstruction(G, \Phi, t, n, i)

9:

assert(n = |\{e \in G.E \mid tid(e) = t\}|)

10:

procedure ExecInstruction(G, \Phi, t, n, i)

11:

switch i do

12:

case i \equiv r := e

13:

\Phi(r) \leftarrow \Phi(e)

14:

case i \equiv r := [e]^{a_{\mathsf{R}}}

15:

\Phi(r) \leftarrow G.val(G_{EN}(G, \langle t, n+1, \mathsf{R}^{a_{\mathsf{R}}}(\Phi(e)) \rangle))

16:

case i \equiv [e_1]^{a_W} := e_2

17:

\operatorname{Gen}(G,\langle t,n+1,\mathsf{W}^{a_{\mathsf{F}}}(\Phi(e_1),\Phi(e_2))\rangle)

18:

case i \equiv fence^{a_F}

19:

G_{EN}(G, \langle t, n+1, F^{a_F} \rangle)

20:

case i \equiv if e goto l

21:

if \Phi(e) \neq 0 then

22:

\Phi(pc) \leftarrow l

23:

if l = \text{error then } \text{Gen}(G, \langle t, n + 1, \text{Error} \rangle)

24:

if l = block then G_{EN}(G, \langle t, n + 1, B \rangle)

25:

procedure Gen(G, a)

26:

assert(a \in G.E)

27:

28:

return a

```

branches where it is set to a specified value when the condition holds. We assume that the two special program counter values error and block do not point to valid instructions.

The interpretation of a thread proceeds in a loop as long as the program counter points to a valid instruction (line 7). In each loop iteration, EXECINSTRUCTION is called to interpret the current instruction (line 9). Under the usual assumption that programs are loop-free (or equivalently, that its loops are unrolled to some specified depth), the **while** loop is guaranteed to terminate<sup>20</sup>. Finally, when the loop finishes, EXECPROGRAM checks that all events of *G* pertaining to thread *t* have been generated (line 10).

EXECINSTRUCTION does a case analysis over the type of the instruction, updating  $\Phi$  as appropriate. For memory accesses, it calls the Gen <sup>20</sup> Technically, this renders algorithm 2.1 a semi-algorithm. helper function, which checks that the next event of the given thread recorded in *G* is the expected one. Whenever a read event *a* is generated, GEN returns the value read by looking up the value written by the write from which *a* reads (line 28). Whenever a branching instruction that jumps to the special error or block address is encountered, EXECINSTRUCTION ensures that the graph contains an Error or a B label, respectively.

We define the executions of a program P under a model M as the set of all M-consistent executions G generated by P; i.e., ExecProgram(P, G)terminates without assertion violations and consistent<sub>M</sub>(G) holds. For example, notice how ExecProgram would terminate without assertion violations for MP and the rightmost graph of Fig. 2.1, denoting that this graph is indeed an execution graph of MP. That execution graph, however, is inconsistent under e.g., SC, since it contains a porf  $\cup$  co  $\cup$  rb cycle.

**Definition 2.4.1** (Program correctness). A program is deemed *erroneous* under a memory model M if its executions under M contain an M-erroneous graph. A program is *correct* if it is not erroneous.

#### 2.4.1 Dependency-Tracking Models

The consistency predicates of certain hardware memory models like ARMv8 or POWER require some additional components in their execution graphs. Indeed, in such architectures, we have to be able to express various instruction *dependencies* in order to reason about consistency.

To account for such models, we define dependency-tracking execution graphs.

**Definition 2.4.2.** A *dependency-tracking execution graph*, *G*, is an execution graph with the following extra relations (all functional on their range):

- the *address-dependency* relation, G.addr ⊆ 𝒫(G.R) × (G.R ∪ G.W), that records the address dependencies of memory accesses.

- the *data-dependency* relation,  $G.data \subseteq \mathcal{P}(G.R) \times G.W$ , that records the data dependencies of writes.

- the *control-dependency* relation, *G*.ctrl ⊆ 𝒫(*G*.R)×*G*.E, that records the control dependencies of events.

We write deps  $\triangleq$  addr  $\cup$  data  $\cup$  ctrl, assume that all dependency edges are included in po, i.e.,  $G.x \subseteq$  po for  $x \in \{addr, data, ctrl\}$ , and also assume that the memory model defines a causal order such that

$(G.rf \cup G.deps)^+ \subseteq G.corder \subseteq G.porf$

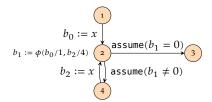

We also modify the EXECPROGRAM by adding a *dependency set*,  $\Delta$  : Reg  $\rightarrow \mathcal{P}(\text{Event})$ , which maps each register to the set of events used to calculate its value (see algorithm 2.2). Dependencies are recorded in  $\Delta$  by EXECPROGRAM in a straightforward manner.

**Remark 2.** One may wonder why the calculation of dependencies happens dynamically via algorithm 2.2 instead of statically. The reason for this is to avoid an over-approximation of dependencies: in the case of a static calculation, and especially in programs with more complicated control flow (e.g., loops, goto statements, etc), a static calculation often results in over-approximating the dependencies of instructions.

To see this, consider the following program:

```

a := x

b := y

if a = 42 goto calcZ

a := b

calcZ :

z := a + 1

```

In the program above (ignoring control dependencies), the z := a+1 instruction data-depends on either x or y, as a will take its value from one of the two respective read statements. Knowing from which one, however, is impossible to determine statically. Since a := x is an instruction reading from shared memory, statically predicting the value of x (which will in turn determine whether a := b is going to be executed) is impossible. Thus, while a static calculation of dependencies would over-approximate by making z := a + 1 depend on both reads, a dynamic calculation has precise knowledge of the write's dependencies.

Algorithm 2.2 Check that *G* is an execution of program *P*

```

1: procedure ExecProgram(P, G)

for \langle t, sprog \rangle \in P do

2:

ExecThread(t, sprog, G)

3:

assert(\forall e \in G.E.P(tid(e)) \neq \bot)

4:

5: procedure ExecThread(t, sprog, G)

\langle t, n, \Phi, \Delta \rangle \leftarrow \langle t, 0, \lambda r. 0, \lambda r. \emptyset \rangle

6:

while i \leftarrow sprog(\Phi(pc)) do

7:

\Phi(pc) \leftarrow \Phi(pc) + 1

8:

ExecInstruction(G, \Phi, \Delta, t, n, i)

9:

assert(n = |\{e \in G.E \mid tid(e) = t\}|)

10:

11: procedure ExecInstruction(G, \Phi, \Delta, t, n, i)

switch i do

12:

case i \equiv r := e

13:

\Phi(r) \leftarrow \Phi(e) \ ; \Delta(r) \leftarrow \Delta(e)

14:

case i \equiv r := [e]^{a_{\mathsf{R}}}

15:

\Phi(r) \leftarrow G.\mathsf{val}(\operatorname{Gen}(G, \langle t, n+1, \mathsf{R}^{a_{\mathsf{R}}}(\Phi(r')) \rangle, \Delta(r'), \emptyset, \Delta(pc)))

16:

\Delta(r) \leftarrow \{a\}

17:

case i \equiv [e_1]^{a_W} := e_2

18:

G_{EN}(G, \langle t, n+1, W^{o_W}(\Phi(e_1), \Phi(e_2)) \rangle, \Delta(e_1), \Delta(e_2), \Delta(pc))

19:

case i \equiv fence^{a_F}

20:

Gen(G, \langle t, n + 1, \mathsf{F}^{a_{\mathsf{F}}}, \emptyset, \emptyset, \Delta(pc) \rangle)

21:

case i \equiv if r goto l

22:

if \Phi(r) \neq 0 then

23:

\Phi(pc) \leftarrow l

24:

if l = \text{error then } \text{Gen}(G, \langle t, n+1, \text{Error}, \emptyset, \emptyset, \Delta(pc) \rangle)

25:

if l = \text{block then } \text{Gen}(G, \langle t, n+1, B, \emptyset, \emptyset, \Delta(pc) \rangle)

26:

\Delta(pc) \leftarrow \Delta(pc) \cup \Delta(r)

27:

28: procedure GEN(G, a, addr, data, ctrl)

assert(a \in G.E)

29:

for x \in \{lab, addr, data, ctrl\} do

30:

assert(G.x(a) = x)

31:

return a

32:

```

Part I

# METATHEORY

# KATER: AUTOMATING WEAK MEMORY MODEL METATHEORY

In this chapter, we present how KATER automates weak memory model metatheory. Before doing so, however, let us briefly discuss the kind of metatheoretic properties KATER automates.

In the past few years, there has been a large body of work on formal definitions of memory models. Along such definitions, there has also been a long line of work trying to establish basic metatheoretic properties of these definitions, answering questions such as:

- Is a given memory model *monotone* with respect to various natural strengthenings, such as inserting a memory fence, merging two threads into a single thread, or, if applicable, strengthening the mode of a memory access (e.g., from release to sequentially consistent)?

- Does a given model admit *local program transformations*, such as reordering of independent memory accesses?

- Given two memory models *A* and *B*, is *A weaker* than *B*? More generally, is a given *compilation scheme* from *A* to *B* (e.g., by inserting certain fences) sound?

- Does a given model rule out "out-of-thin-air" (OOTA) outcomes? That is, does it rule out dependency cycles?

Using KATER, we can automate the questions above for declarative models that are expressed as emptiness, acyclicity, and irreflexivity constraints over relational algebra terms.

The key observation that allows us to do so is that the fragment of relational algebra used in most definitions of memory models (e.g., SC, TSO, PSO, POWER, ARMv8, RC11, IMM) corresponds closely to *Kleene Algebra with Tests* (KAT)<sup>21</sup>, an extension of regular expressions with a Boolean algebra over a collection of predicates describing a state.

Leveraging this insight, these questions can be automated as follows. First, we show that checking whether one model is weaker than another can naturally be expressed as a language inclusion problem that can be decided using finite-state automata (§3.3). While the constraints themselves are not directly encodable in vanilla KAT, memory model inclusion can be reduced to proving entailments between KAT formulae, which is decidable for simple classes of entailments. Then, using this result, we also show how to check monotonicity, correctness of program transformations, correctness of compilation mappings, lack of OOTA behaviors, prefix-closedness, and extensibility<sup>22</sup> <sup>21</sup> "Kleene Algebra with Tests" [Koz97]

<sup>22</sup> Properties like lack of OOTA, prefix-closedness and extensibility are useful for model checking and are explained in detail in §5. (Section 3.4 to 3.8).

Before explaining how KATER works, we start with some background on regular languages and KAT (Section 3.1 and 3.2). Readers familiar with these concepts may skip these sections.

#### 3.1 REGULAR LANGUAGES AND FINITE STATE AUTOMATA

We fix an *alphabet* (i.e., a finite non-empty set)  $\Sigma$ . A *language L* is a set of words in  $\Sigma^*$ . We use *a*, *b*, ... to range over  $\Sigma$ , and *u*, *v*, *w*, ... to range over  $\Sigma^*$ .

A *non-deterministic finite automaton* (NFA) over  $\Sigma$  is a tuple  $\langle Q, \delta, S, F \rangle$ where Q is a finite set of states,  $S \subseteq Q$  is a set of initial states,  $F \subseteq Q$  is a set of final states, and  $\delta : Q \times \Sigma \to \mathcal{P}(Q)$  is the transition function which, given a state  $q \in Q$  and a letter  $a \in \Sigma$ , returns the set of possible next states  $\delta(q, a)$ . By abuse of notation, we extend the domain of the transition function to take as parameters a set of states and a word as follows:  $\delta(S, a) \triangleq \bigcup_{a \in S} \delta(q, a), \delta(S, \epsilon) \triangleq S$ , and  $\delta(S, aw) \triangleq \delta(\delta(S, a), w)$ .

The *language accepted* by an NFA contains all words for which there is a path from an initial state of the NFA to a final state:  $L(\langle Q, \delta, S, F \rangle) \triangleq \{w \in \Sigma^* \mid \delta(S, w) \cap F \neq \emptyset\}$ . Two NFAs are *language-equivalent* iff they accept the same language.

A *deterministic finite automaton* (DFA) is an NFA that has exactly one initial state and where for every  $q \in Q$  and  $a \in \Sigma$ , the set  $\delta(q, a)$  contains at most one element. The *powerset construction* transforms an NFA  $\langle Q, \delta, S, F \rangle$  over  $\Sigma$  into a language-equivalent DFA  $\langle \mathcal{P}(Q), \delta_p, \{s_0\}, F' \rangle$  where  $s_0 \triangleq S, F' \triangleq \{s \subseteq Q \mid s \cap F \neq \emptyset\}$ , and  $\delta_p(s, a) \triangleq \{\delta(s, a)\}$ .

A *regular language* is one described by a regular expression or equivalently one accepted by an NFA. There are standard conversions from regular expressions to NFAs and vice versa. Regular languages are closed under:

- *union*  $(L_1 \cup L_2)$ ;

- concatenation  $(L_1; L_2)$ ;

- repetition (L\*);

- *intersection*  $(L_1 \cap L_2)$ , by the product construction on NFAs:  $\langle Q_1 \times Q_2, \delta_P, S_1 \times S_2, F_1 \times F_2 \rangle$  where  $\delta_P(\langle q_1, q_2 \rangle) \triangleq \delta_1(q_1) \times \delta_2(q_2)$ ;

- *complementation*  $(\overline{L})$ , by conversion to DFA and complementing the set of final states;

- *reversal* (*L*<sup>-1</sup>), by swapping initial and final states in NFA, and reversing the transitions;

- substitution (L[L<sub>1</sub>/a<sub>1</sub>,...,L<sub>n</sub>/a<sub>n</sub>]), by replacing all a<sub>i</sub> transitions of an NFA with automata accepting L<sub>i</sub>;

- *rotational closure* (ROT(*L*)  $\triangleq \{uv \mid vu \in L\}$ ), which can be computed on an NFA *N* as  $\bigcup_{q \in N.Q} \text{After}_q$ ; Before<sub>q</sub> where After<sub>q</sub> is the NFA obtained from *N* by making *q* be its only initial state and Before<sub>q</sub> is the NFA obtained from *N* by making *q* be the only final state; and

- *deduplication closure* (DEDUP(L)  $\triangleq$  { $w \in \Sigma^* \mid \exists n. w^n \in L$ }), which can be computed on an NFA<sup>23</sup>.

Finally, inclusion and equivalence of regular languages are decidable (PSPACE-complete) by noting that  $L_1 \subseteq L_2 \Leftrightarrow L_1 \cap \overline{L_2} = \emptyset$ . Given that the expensive part of this inclusion checking is the DFA conversion as part of the complementation of  $L_2$ , there are algorithms<sup>24</sup> that avoid performing the DFA conversion upfront and perform it "on demand" while traversing the NFA of  $L_1$ .

#### 3.2 KLEENE ALGEBRA WITH TESTS (KAT)

*Kleene algebra with tests*<sup>25</sup> (KAT) extends regular languages with a set of *tests*, over which there is a Boolean algebra.

Let Predicate be a finite set of primitive predicate symbols and Relation be a finite set of primitive relation symbols. KAT tests (t) and expressions (e) are given by the following grammar:

$$t ::= p \mid \text{true} \mid \text{false} \mid t_1 \cup t_2 \mid t_1 \cap t_2 \mid t$$

$$e ::= [t] \mid r \mid e_1 \cup e_2 \mid e_1; e_2 \mid e^*$$

where  $p \in$  Predicate ranges over primitive predicates and  $r \in$  Relation over primitive relations. KAT tests contain the usual Boolean operators, while KAT expressions contain tests, relations, union, sequencing, and iteration. Tests allow us to express the empty relation  $\emptyset \triangleq$  [false] and the identity relation id  $\triangleq$  [true]. Moreover, as usual, reflexive closure is expressed as  $e^? \triangleq e \cup$  id and transitive closure as  $e^+ \triangleq e$ ;  $e^*$ .

KAT expressions are standardly interpreted as languages of *guarded* words, that is, alternating sequences of satisfiable tests and relations starting and ending with a test,  $t_1r_1t_2r_2...t_nr_nt_{n+1}$  for some  $n \ge 0$ . We write L(*e*) for the language induced by a KAT expression *e*.

KAT expressions can equivalently be interpreted as binary relations over a certain universe. In our context, we use execution graphs as models. Recall from §2.2 that each execution graph *G* consists of a set *G*.E of nodes, called *events*, and interpretations of primitive tests as subsets of events and of primitive relations as binary relations on events:

$$\llbracket.\rrbracket_G : \mathsf{Predicate} \to \mathcal{P}(G.\mathsf{E}) \qquad \llbracket.\rrbracket_G : \mathsf{Relation} \to \mathcal{P}(G.\mathsf{E} \times G.\mathsf{E})$$

<sup>23</sup> Is the power of a regular language regular? Is the root of a regular language regular?

[*Fil*]

<sup>24</sup> "Checking NFA equivalence with bisimulations up to

congruence" [BP13]

<sup>25</sup> "Kleene Algebra with Tests" [Koz97] This interpretations are extended to KAT tests and expressions in the obvious way:

$$\begin{bmatrix} \mathsf{true} \end{bmatrix}_G \triangleq G.\mathsf{E} \qquad \qquad \begin{bmatrix} \mathsf{false} \end{bmatrix}_G \triangleq \emptyset \qquad \qquad \begin{bmatrix} \bar{t} \end{bmatrix}_G \triangleq G.\mathsf{E} \setminus \begin{bmatrix} t \end{bmatrix}_G \\ \begin{bmatrix} t_1 \cup t_2 \end{bmatrix}_G \triangleq \begin{bmatrix} t_1 \end{bmatrix}_G \cup \begin{bmatrix} t_2 \end{bmatrix}_G \qquad \qquad \begin{bmatrix} t_1 \cap t_2 \end{bmatrix}_G \triangleq \begin{bmatrix} t_1 \end{bmatrix}_G \cap \begin{bmatrix} t_2 \end{bmatrix}_G \qquad \qquad \begin{bmatrix} [t] \end{bmatrix}_G \triangleq \begin{bmatrix} [t] \end{bmatrix}_G \\ \begin{bmatrix} e_1 \cup e_2 \end{bmatrix}_G \triangleq \begin{bmatrix} e_1 \end{bmatrix}_G \cup \begin{bmatrix} e_2 \end{bmatrix}_G \qquad \qquad \begin{bmatrix} e_1 ; e_2 \end{bmatrix}_G \triangleq \begin{bmatrix} e_1 \end{bmatrix}_G ; \begin{bmatrix} e_2 \end{bmatrix}_G \qquad \qquad \begin{bmatrix} e^* \end{bmatrix}_G \triangleq \begin{bmatrix} e \end{bmatrix}_G^*$$

On top of KAT expressions, KAT *formulas* are defined by the following grammar:

$$\phi ::= e_1 \subseteq e_2 \mid \neg \phi \mid \phi_1 \land \phi_2 \mid \phi_1 \lor \phi_2 \mid \phi_1 \Rightarrow \phi_2 \mid \phi_1 \Leftrightarrow \phi_2$$

KAT formulas are interpreted as sets of execution graphs in the standard way: for example,  $\llbracket e_1 \subseteq e_2 \rrbracket \triangleq \{G \mid \llbracket e_1 \rrbracket_G \subseteq \llbracket e_2 \rrbracket_G\}$  and  $\llbracket \phi_1 \Rightarrow \phi_2 \rrbracket \triangleq \{G \mid G \in \llbracket \phi_1 \rrbracket \Rightarrow G \in \llbracket \phi_2 \rrbracket\}$ . The interpretation is extended to sets of KAT formulas in the obvious way:  $\llbracket \Phi \rrbracket \triangleq \bigcap_{\phi \in \Phi} \llbracket \phi \rrbracket$ . We say that a KAT formula  $\phi$  holds, denoted by  $\vdash \phi$ , if  $\llbracket \phi \rrbracket$  is equal to the set of all graphs. We write  $\Phi \vdash \phi$  if  $\llbracket \Phi \rrbracket \subseteq \llbracket \phi \rrbracket$ .

<sup>26</sup> "Kleene Algebra with Tests: Completeness and Decidability" [KS96] Inclusion between KAT expressions (i.e.,  $\vdash e_1 \subseteq e_2$ ) is PSPACEcomplete, and remains so even under basic assumptions like emptiness of a KAT expression ( $e = \emptyset$ ) or transitivity of a primitive relation ( $r ; r \subseteq r$ )<sup>26</sup>. Inclusion and equivalence can be decided either by algebraic techniques or by reduction to finite state automata. In the latter case, it is convenient to first convert the automata into a normal form that accepts only guarded words, and then apply standard ways of checking language inclusion/equivalence between automata.

Conversion into the normal form has to ensure: (1) that each automaton state has incoming edges being predicates and outgoing edges being relations (or the other way round), (2) that all outgoing edges from initial states are predicate edges, and (3) that all incoming edges to accepting states are predicate edges. To do so, any states with both kinds of incoming and outgoing transitions have to be duplicated and suitably restricted: adjacent predicate transitions of the form  $[p_1]$ ;  $[p_2]$  are replaced with single composite transitions of the form  $[p_1 \cap p_2]$ , while adjacent transitions with relations are moved apart by adding a dummy [true] transition between them. Similarly, outgoing relation edges from initial states have to be prefixed with a dummy [true] transition, and conversely incoming relation edges to accepting states have to be postfixed with a [true] transition.

#### 3.3 MEMORY MODELS AS KAT CONSTRAINTS

Axiomatic memory models can be formulated as a single emptiness constraint and a single irreflexivity constraint over KAT. For this purpose, we extend KAT formulas with a new construct irreflexive(*e*) with semantics [[irreflexive(*e*)]]  $\triangleq \{G \mid \nexists a. \langle a, a \rangle \in [\![e]\!]_G \}$ . Models with mul-

tiple such constraints can be encoded because of the following basic relational algebra properties:

$e_1 = \emptyset \land e_2 = \emptyset \Leftrightarrow e_1 \cup e_2 = \emptyset$ irreflexive( $e_1$ )  $\land$  irreflexive( $e_2$ )  $\Leftrightarrow$  irreflexive( $e_1 \cup e_2$ )

Similarly, acyclicity constraints can be encoded as  $acyclic(e) \triangleq irreflexive(e^+)$ .

Formally, a *memory model* M is a pair of KAT expressions  $\langle e_{\emptyset}, e_{irr} \rangle$ , interpreted as a collection of execution graphs

$\llbracket \langle e_{\emptyset}, e_{irr} \rangle \rrbracket \triangleq \llbracket e_{\emptyset} = \emptyset \land irreflexive(e_{irr}) \rrbracket$

We say that a memory model  $M_1$  is *stronger* than another model  $M_2$  (and  $M_2$  is *weaker* than  $M_1$ ) if  $[M_1] \subseteq [M_2]$ . Two models are equivalent if they are both stronger and weaker than each other.

#### 3.4 ADDING DOMAIN-SPECIFIC ASSUMPTIONS

To be able to prove interesting metatheoretic properties, we need to equip KATER with some domain-specific assumptions. We go over these assumptions using some rather simple examples.

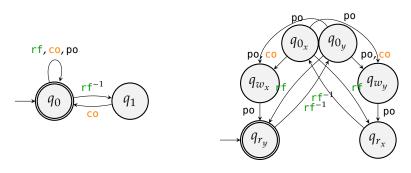

#### 3.4.1 Extended Coherence Order

We begin with a rather simple example. In addition to the two basic relations of §2.2, Lahav et al.<sup>27</sup> define the *extended coherence order* as the transitive closure of rf, co and rb:  $eco \triangleq (rf \cup co \cup rb)^+$ . Observe that eco can equivalently be expressed without the transitive closure as  $rf \cup (co \cup rb)$ ;  $rf^?$ .

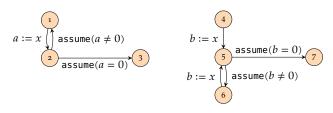

Suppose that we want to automatically verify the latter claim. The idea is to think of the two different formulations of **eco** as regular expressions over the alphabet {rf, rf<sup>-1</sup>, co}, and then check for equivalence between them. In KATER, we would write the following<sup>28</sup>:

```

declare rf rf<sup>-1</sup> co

let fr = rf<sup>-1</sup>;co

let eco<sub>1</sub> = (rf \cup co \cup fr)<sup>+</sup>

let eco<sub>2</sub> = rf \cup (co \cup fr);rf<sup>?</sup>

assert eco<sub>1</sub> = eco<sub>2</sub>

```

With this input, KATER immediately returns a counterexample saying that  $eco_1$  accepts the string rf; rf but  $eco_2$  does not.

We clearly want to dismiss this counterexample because rf takes us from a write to a read, and we know that an event cannot be both a read and a write. One way to do so is to tell KATER that the rf does not compose with itself: <sup>27</sup> "Repairing sequential consistency in C/C++11" [Lah+17]

<sup>28</sup> This a pretty-printed version of the actual input syntax, which uses ASCII (e.g., | for union and <= for inclusion). assume rf;rf = 0

Adding assumptions makes the language inclusion/equivalence problem more challenging. For some very simple kinds of assumptions, such as ones of the form  $e = \emptyset$  (where *e* is a KAT expression), language inclusion remains decidable.

**Proposition 1** ([KS96, Theorems 6 and 9]). Let e,  $e_1$ , and  $e_2$  be KAT expressions. Then,  $e = \emptyset \vdash e_1 \subseteq e_2$  if and only if  $\vdash e_1 \subseteq e_2 \cup \text{Relation}^*$ ; e; Relation<sup>\*</sup>.

This time KATER returns rf; co as a counterexample, which we dismiss for the same reason. And since we are at it, let's also state that co;  $rf^{-1} = \emptyset$ .

```

assume rf;co = 0

assume co;rf<sup>-1</sup> = 0

```

Next comes a more interesting counterexample: **co**;**co**. Here, the equivalence proof relies upon **co** being transitive, but KATER has not way of knowing that. So, let's add the assumption:

```

assume co;co \subseteq co

```

Such transitivity assumptions can also be eliminated completely: to check that  $\Phi \vdash \phi$  under the additional assumption that a primitive relation *r* is transitive, we can replace all uses of *r* in  $\Phi$  and  $\phi$  with *r*<sup>+</sup>.

**Proposition 2.** Let  $\phi$  be a KAT formula,  $\Phi$  be a set of KAT formulas, and *r* be a primitive relation symbol. Then,  $\Phi$ , *r* ; *r*  $\subseteq$  *r*  $\vdash \phi$  if and only if  $\Phi[r^+/r] \vdash \phi[r^+/r]$ .

Running KATER now reveals another interesting counterexample: rf;  $rf^{-1}$ ; co. What is missing is the knowledge that  $rf^{-1}$  is functional: every read reads from exactly one write. Adding the missing assumption

```

assume rf; rf^{-1} \subseteq id

```

allows KATER to complete the equivalence proof and report success.