# Scaling Up Relaxed Memory Verification with Separation Logics

Dissertation zur Erlangung des Grades des Doktors der Ingenieurwissenschaften der Fakultät für Mathematik und Informatik der Universität des Saarlandes

vorgelegt von Hoang-Hai Dang

Saarbrücken, 2024

TAG DES KOLLOQUIUMS 10. September, 2024

DEKAN DER FAKULTÄT FÜR MATHEMATIK UND INFORMATIK Prof. Dr. Roland Speicher

Prüfungsausschuss

| Vorsitzender:             | Prof. Dr. Sven Apel    |  |

|---------------------------|------------------------|--|

| Gutachter:                | Prof. Dr. Derek Dreyer |  |

|                           | Prof. Dr. Mark Batty   |  |

|                           | Dr. Viktor Vafeiadis   |  |

| Akademischer Mitarbeiter: | Dr. Léo Stefanesco     |  |

|                           |                        |  |

### Abstract

Reasoning about concurrency in a realistic, non-toy language like C/C++ or Rust, which encompasses many interweaving complex features, is very hard. Yet, *realistic* concurrency involves relaxed memory models, which are significantly harder to reason about than the simple, traditional concurrency model that is sequential consistency. To *scale up* verifications to realistic concurrency, we need a few ingredients: (1) strong but abstract reasoning principles so that we can avoid the too tedious details of the underlying concurrency model; (2) modular reasoning so that we can compose smaller verification results into larger ones; (3) reasoning extensibility so that we can derive new reasoning principles for both complex language features and algorithms without rebuilding our logic from scratch; and (4) machine-checked proofs so that we do not miss potential unsoundness in our verifications. With these ingredients in hand, a logic designer can flexibly accommodate the intricacy of relaxed memory features and the ingenuity of programmers who exploit those features.

In this dissertation, I present how to develop strong, abstract, modular, extensible, and machinechecked separation logics for realistic relaxed memory concurrency in the Iris framework, using multiple layers of abstractions. I report two main applications of such logics: (i) the verification of the Rust type system with a relaxed memory model, where relaxed memory effects are encapsulated behind the safe interface of libraries and thus are not visible to clients, and (ii) the compositional specification and verification of relaxed memory libraries, in which relaxed memory effects are exposed to clients.

### Zusammenfassung

Programmverifikation von nebenläufige Programmen in einer realistischen Programmiersprache wie C/C++ oder Rust, die viele komplexe, miteinander verflochtene Sprachkonstrukte enthält, ist sehr schwierig. Realistische nebenläufige Programme basieren auf *schwachen Speicherkonsistenzmodellen*, in denen sich die Beweisführung im Vergleich zum traditionellen, sequentiellen Speicherkonsistenzmodell (SC) erheblich schwieriger gestaltet. Um die Verifikation solcher realistischen nebenläufigen Programme zu ermöglichen benötigen wir mehrere Voraussetzungen: (1) starke Beweisregeln die die mühsamen Details des zugrundeliegenden Speicherkonsistenzmodells abstrahieren, (2) modulare Beweistechniken die es erlauben, die Verifikation in kleinere, mundgerechte Beweise aufzuteilen, (3) eine erweiterbare Verifikationslogik, in der neue Beweistechniken hinzugefügt werden können, ohne die Korrektheit der gesamten Logik erneut beweisen zu müseen (4) maschinengeprüfte Beweise, die die Korrektheit der Logik und der durchgeführten Beweise garantiert. Mit diesen Voraussetzungen kann ein Logikdesigner die Komplexität des schwachen Speicherkonsistenzmodells und den Einfallsreichtum der Programmierer, die sich dessen Funktionenen zu Nutze machen, flexibel berücksichtigen.

In dieser Dissertation stelle ich vor, wie man starke, abstrakte, modulare, erweiterbare und maschinengeprüfte Separationslogiken für realistische schwache Speicherkonsistenz in dem Framework Iris mit Hilfe von mehreren Abstraktionsebenen erstellen kann. Ich berichte über zwei Hauptanwendungen dieser Logiken: (i) die Verifikation des Typsystems von Rust auf Basis eines schwachen Speicherkonsistenzmodells, bei dem die Auswirkungen schwacher Speicherkonsistenz hinter der sicheren Programmschnittstelle abstrahiert und somit für Clients unsichtbar sind, und (ii) die modulare Spezifikation und Verifikation von Programmbibliotheken mit schwacher Speicherkonsistenz, bei denen die Auswirkungen schwacher Speicherkonsistenz für Clients sichtbar sind.

## Acknowledgments

My PhD work was long and difficult. Fortunately, in the end, it has been a fruitful journey—I would not have been able to image where I am today. And for that, I am grateful to be able to work with and learn from ingenious and amazing people during that time.

I would like to deeply thank my advisor, Derek Dreyer, for his giving me the opportunity and support to embark on this arduous journey. Derek has always managed to surround himself with the most interesting research problems, and, as a result, I as his student, had multiple chances to work with some of those. I remember my first project with him was about using the very first version of Iris to encode high-order reasoning principles for continuations. I started the project without knowledge on Iris and reasoning about continuations, but Derek had encouraged and helped me through it. For that first project, I would also additionally like to thank David Swasey for his various guiding discussions, even though most did not make sense to me at the time. After that, Derek put me on the true beginning of my PhD life: the iGPS project. I still do not understand how or if Derek had foreseen that I could survive that! With some luck, I got through it and learnt a lot, and for that, I also would like to thank Janno Kaiser, Ori Lahav, and Viktor Vafeiadis for their teaching me about relaxed memory and Coq. After the success of iGPS, I have had the chances to work on more difficult problems, and Derek had always been there for me. I still remember the night of 2018, when we were running towards the deadline of the PLDI submission, and Derek found the bug in the race detector of ORC11, and we had to decide to submit the RustBelt Relaxed paper later. Thank you Derek, for always being vigilant and on the point.

I thank Mark Batty and Viktor Vafeadis for serving as reviewers of my dissertation, and Sven Apel as chair and Léo Stefanesco as academic member of my committee. I would also like to thank all of the collaborators that I have worked with—without them, I would have achieved nothing. I would like to thank Jacques-Henri Jourdan, Ralf Jung, Jeehoon Kang, Azalea Raad, William Mansky, Robbert Krebbers, Jaehwang Jung, Jaemin Choi, Duc-Than Nguyen, Joshua Yanovski, Lennard Gäher, Michael Sammler, and Simon Spies. I am forever grateful to Rose Hoberman for her teaching of English, scientific writing, and communication skills.

Living in Germany would me impossible without my friends. I thank my dear Vietnamese friends in Saarbrücken, in Luxembourg, in Vienna, and in Antibes. I would also my friends that I got to know at MPI-SWS: Heiko Becker, Debasmita Lohar, Reinhard Munz, Ezgi Cicek, Rodolphe Lepigre, Gaurav Parthasarathy, and Raphaël Monat.

Last but not least, I thank my beloved family: my parents and my big brother, for having also been there for me, across the continents. Without them, I would not have even arrived in this continent and would not have met so many great people. I dedicate this dissertation to my mother and my father.

Saarbrücken, September 2024

Đặng Hoàng Hải

Contents

| Ab  | ostract                                                                                                                                                                                                                                                         | iii            |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Zu  | sammenfassung                                                                                                                                                                                                                                                   | iii            |

| Ac  | knowledgments                                                                                                                                                                                                                                                   | v              |

| Co  | ontents                                                                                                                                                                                                                                                         | ix             |

| Lis | st of Figures                                                                                                                                                                                                                                                   | xiii           |

| Lis | st of Tables                                                                                                                                                                                                                                                    | xv             |

| Gl  | ossary                                                                                                                                                                                                                                                          | cvii           |

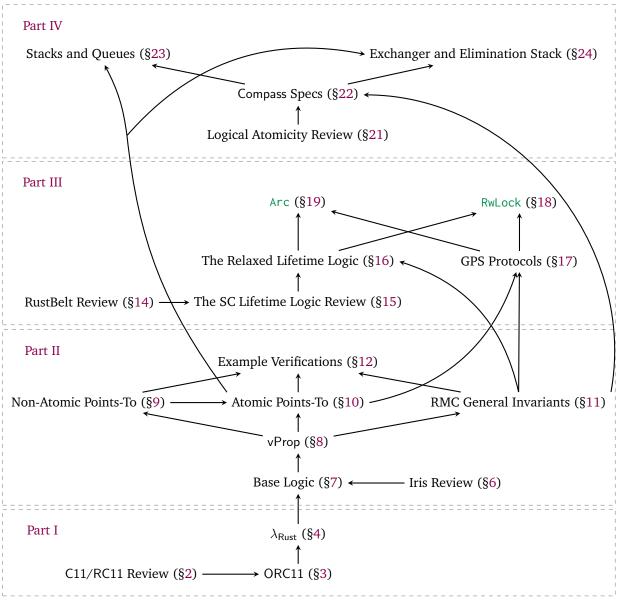

| 1   | Introduction1.1Reasoning about Relaxed Memory Concurrency1.2RustBelt Relaxed: Verifying the Soundness of Rust's Type System in RMC1.3Compass: Strong and Compositional Specifications of Relaxed-Memory Libraries1.4Structure1.5Publications and Collaborations | .3<br>.5<br>.8 |

| I   | OPERATIONAL SEMANTICS FOR RELAXED MEMORY                                                                                                                                                                                                                        | 11             |

| 2   | Background: Relaxed Memory Models         2.1       C11, Intuitively         2.2       RC11, Formally         ORC11: Operational Repaired C11         3.1       Understanding Relaxed Memory with Views                                                         | 17<br>27<br>27 |

|     | <ul> <li>3.2 Basic Machine State Definitions</li> <li>3.3 View-based RMC Semantics</li> <li>3.4 The Data-Race Detector</li> <li>3.5 Comparison with iGPS Race Detector</li> <li>3.6 The Correspondence between RC11 and ORC11</li> </ul>                        | 34<br>39<br>42 |

| 4   | The Relaxed $\lambda_{Rust}$ Language         4.1       Language Syntax         4.2       Language Expression Reductions         4.3       The Complete Operational Semantics of Relaxed $\lambda_{Rust}$                                                       |                |

| 5   | Related Work                                                                                                                                                                                                                                                    | 57             |

| II  | SEPARATION LOGIC FOR RELAXED MEMORY                                                                                                                                                                                                                             | 59             |

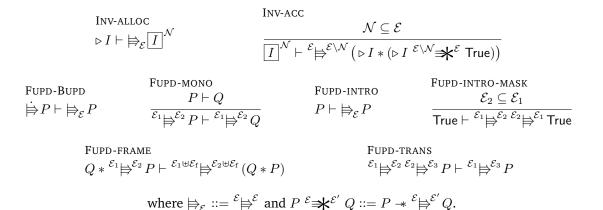

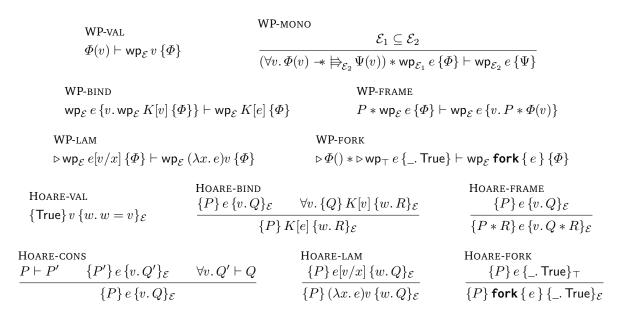

| 6   | More Background: Iris, A Framework for Concurrent Separation Logics6.1Basic Rules6.2Ghost State and Resource Algebras6.3Invariants and Fancy Updates                                                                                                            |                |

|     | 6.4 Hoare Triples                                            |      |

|-----|--------------------------------------------------------------|------|

|     | 6.5 Adequacy                                                 |      |

|     | 6.6 Some Common Rules for WPs and Hoare Triples              |      |

|     | 6.7 Weakest Pre-conditions and Invariants                    |      |

|     | 6.8 Properties of Propositions                               |      |

|     | 6.9 The Method of Fictional Separation                       |      |

|     | 6.10 The Physical State Interpretation                       |      |

|     | 6.11 An Instantiation Example for Simple Heaps               | 75   |

| 7   | A Base Logic for RMC in Iris                                 | 79   |

|     | 7.1 Thread-local Configurations as Expressions               | 79   |

|     | 7.2 Basic Local Assertions for View-based RMC                | 81   |

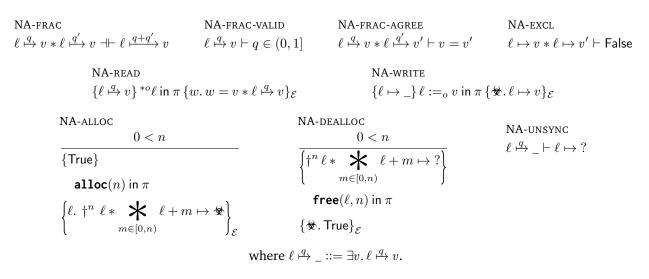

|     | 7.3 Primitive Memory Rules                                   | 84   |

|     | 7.4 Resource Algebras for Basic Local Assertions             | 92   |

|     | 7.5 State Interpretation                                     | 93   |

|     | 7.6 Proofs of Some Primitive Rules and Adequacy              | 96   |

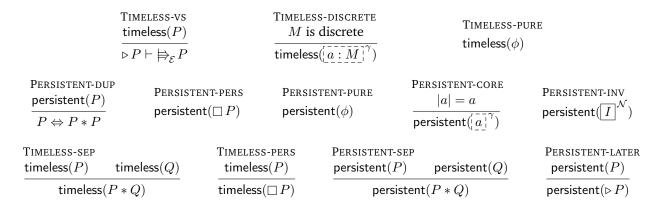

| 8   | vProp: View-monotone Predicates                              | 99   |

| Ŭ   | 8.1 View-monotone Predicates                                 |      |

|     | 8.2 Model of iRC11 Weakest Pre-conditions                    |      |

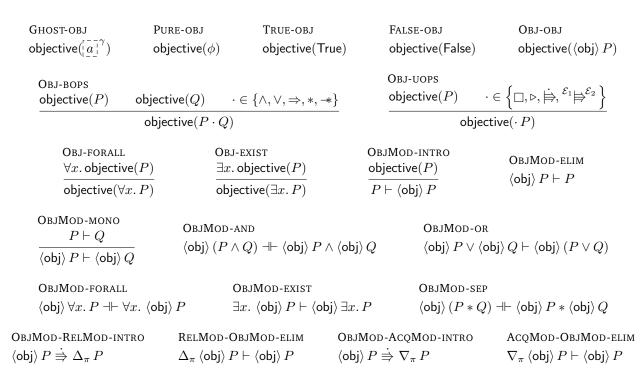

|     |                                                              | 102  |

|     | 8.4 Objective Propositions and The Objective Modality        |      |

|     | 8.5 View-explicit Modalities                                 |      |

|     | 1                                                            | 109  |

| _   |                                                              |      |

| 9   | Non-Atomic Points-To                                         | 111  |

|     | • • • • • • • • • • • • • • • • • • • •                      | 111  |

|     | 9.2 The Model of Non-Atomic Points-To                        | 112  |

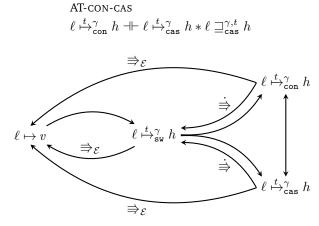

| 10  | Atomic Points-To                                             | 115  |

|     | 10.1 The Interface of the Atomic Points-To Assertion         | 116  |

|     | 10.2 The Model of the Atomic Points-To Assertion             | 126  |

| 11  | Invariants in Relaxed Memory                                 | 133  |

|     | 11.1 Objective Invariants                                    |      |

|     | 11.2 Cancelable Invariants                                   | 136  |

|     | 11.3 Non-Atomic Invariants                                   | 143  |

|     |                                                              | 1 10 |

| 12  | Example Verifications with iRC11                             | 145  |

|     | 12.1 Release-Acquire Message-Passing                         | 145  |

|     | 12.2 Release-Acquire Message-Passing with Reclamation        | 149  |

|     | 12.3 Spawn and Join                                          | 154  |

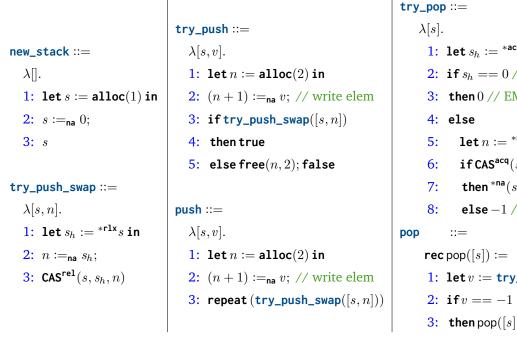

|     | 12.4 A Release-Acquire Treiber Stack                         | 156  |

| 13  | Related Work                                                 | 167  |

| III | RUSTBELT MEETS RELAXED MEMORY                                | 171  |

| 14  | Challenge: RustBelt and Relaxed Memory                       | 173  |

| - 1 | 14.1 Task 1: Re-prove the Safety of Rust Libraries under RMC | 174  |

|     |                                                              | 176  |

|     |                                                              |      |

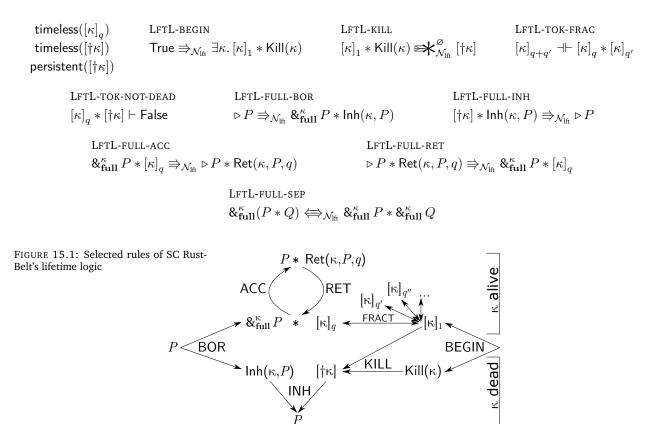

| 15 The Lifetime Logic of SC RustBelt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 79                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 15.1 Borrowing in Rust                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 79                                                                                                                               |

| 15.2 The Lifetime Logic Primer, in SC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 81                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 87                                                                                                                               |

| 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 87                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 91                                                                                                                               |

| 16.3 Adaption of the Lifetime Logic's Model in iRC11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 95                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 01                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 01                                                                                                                               |

| 17.2 Middleware GPS Protocols in iRC11 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                  |

| 17.3 The Model of GPS Protocols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 21                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ~-                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 25                                                                                                                               |

| 18.1 RMC Implementation of a Reader-Writer Lock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                  |

| 18.2 The Semantic Model of the Reader-Writer Lock Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                  |

| 18.3 Proof Sketches of the Library's Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 33                                                                                                                               |

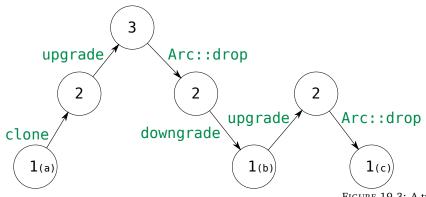

| 19 Verification of Arc 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 37                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37<br>37                                                                                                                         |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 39                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 45                                                                                                                               |

| 19.4 Insufficient Synchronization in get_mut    24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 49                                                                                                                               |

| 20 Related Work 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 51                                                                                                                               |

| 20 Related Work 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 51                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                  |

| IV COMPASS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 53                                                                                                                               |

| IV COMPASS 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 53                                                                                                                               |

| 21 Background: Strong Specifications with Logical Atomicity 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 53<br>57                                                                                                                         |

| 21 Background: Strong Specifications with Logical Atomicity 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                  |

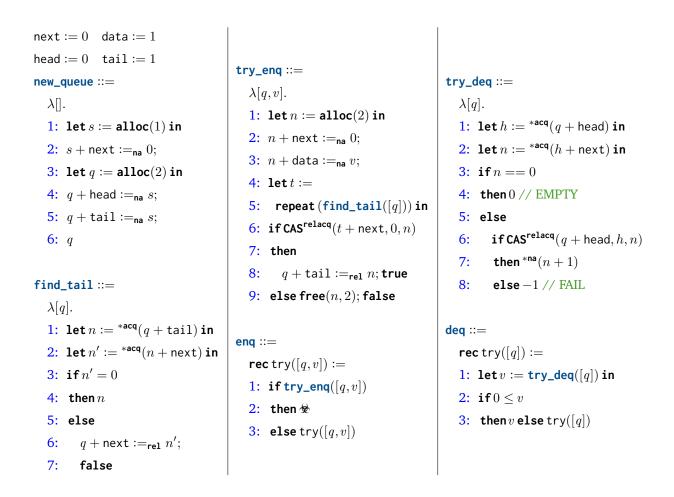

| <b>21 Background: Strong Specifications with Logical Atomicity</b> 25         21.1 Sequential Specifications for Queues       25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 57                                                                                                                               |

| <b>21 Background: Strong Specifications with Logical Atomicity</b> 25         21.1 Sequential Specifications for Queues       25         21.2 SC Specifications with Logical Atomicity       25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 57<br>57                                                                                                                         |

| <b>21 Background: Strong Specifications with Logical Atomicity</b> 22         21.1 Sequential Specifications for Queues       22         21.2 SC Specifications with Logical Atomicity       22         21.3 Logically Atomic Specifications in RMC with Views       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 57<br>57<br>58                                                                                                                   |

| 21 Background: Strong Specifications with Logical Atomicity       23         21.1 Sequential Specifications for Queues       24         21.2 SC Specifications with Logical Atomicity       25         21.3 Logically Atomic Specifications in RMC with Views       26         22 Strong Compass Specifications with Richer Partial Orders       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 57<br>57<br>58<br>60<br>63                                                                                                       |

| 21 Background: Strong Specifications with Logical Atomicity       25         21.1 Sequential Specifications for Queues       26         21.2 SC Specifications with Logical Atomicity       27         21.3 Logically Atomic Specifications in RMC with Views       26         22 Strong Compass Specifications with Richer Partial Orders       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 57<br>57<br>58<br>60                                                                                                             |

| 21 Background: Strong Specifications with Logical Atomicity       22         21.1 Sequential Specifications for Queues       23         21.2 SC Specifications with Logical Atomicity       24         21.3 Logically Atomic Specifications in RMC with Views       26         22 Strong Compass Specifications with Richer Partial Orders       26         22.1 Graph-Based Specs to Encode Partial Orders       26         22.2 Weaker Specs by Abandoning Abstract States       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 57<br>57<br>58<br>60<br>63<br>63                                                                                                 |

| 21 Background: Strong Specifications with Logical Atomicity       22         21.1 Sequential Specifications for Queues       22         21.2 SC Specifications with Logical Atomicity       22         21.3 Logically Atomic Specifications in RMC with Views       22         22 Strong Compass Specifications with Richer Partial Orders       22         22.1 Graph-Based Specs to Encode Partial Orders       22         22.2 Weaker Specs by Abandoning Abstract States       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 57<br>57<br>58<br>60<br>63<br>63                                                                                                 |

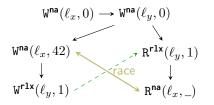

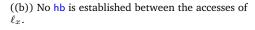

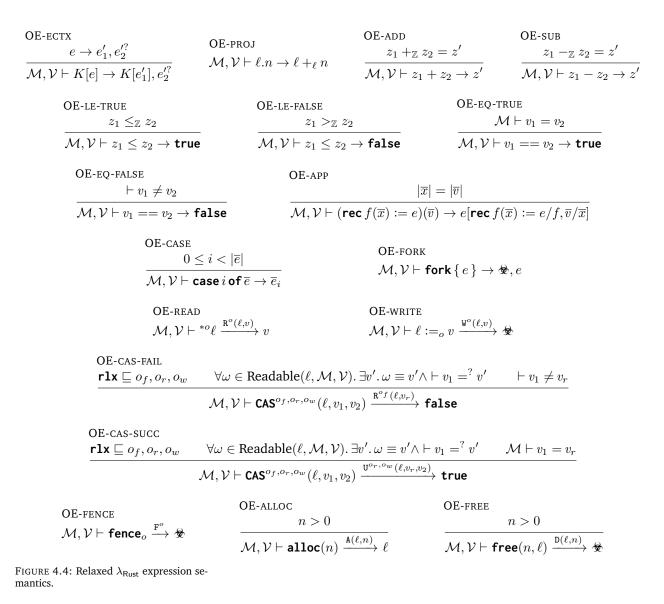

| 21 Background: Strong Specifications with Logical Atomicity       22         21.1 Sequential Specifications for Queues       22         21.2 SC Specifications with Logical Atomicity       22         21.3 Logically Atomic Specifications in RMC with Views       22         22 Strong Compass Specifications with Richer Partial Orders       22         22.1 Graph-Based Specs to Encode Partial Orders       22         22.2 Weaker Specs by Abandoning Abstract States       22         22.3 Implementing Compass Specs in iRC11       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 57<br>57<br>58<br>60<br>63<br>63<br>63<br>68<br>69                                                                               |