# **Proceedings of the Work-in-Progress Session**

of the 20th IEEE Real-Time and Embedded Technology and Applications Symposium

© Copyright 2014 Max Planck Institute for Software Systems. All rights reserved. The copyright of this collection is with the Max Planck Institute for Software Systems. The copyright of the individual articles remains with their authors. Cover photo: B. Brandenburg.

# Message from the Work-in-Progress Chair

The Work-in-Progress (WiP) session at RTAS 2014 is dedicated to new and on-going research in the field of real-time and embedded systems. The WiP session is an integral and important part of the RTAS program, as it exposes promising research directions to a wider audience and provides researchers with an opportunity to discuss evolving and early-stage ideas, and to solicit feedback from the real-time systems community at large.

First of all, I would like to thank the authors for submitting their work, and the members of the program committee for their quick and helpful reviews. This year, the WiP track received a total of 17 high-quality submissions, each of which was reviewed by three members of the program committee. After a final online discussion round, twelve excellent papers were selected for presentation at the WiP session.

The resulting technical program covers a broad range of topics—spanning from, on the one hand, timing analysis, schedulability analysis, and mapping heuristics for many-core platforms to, on the other hand, air data estimation in UAVs, a novel kernel design for mixed-criticality systems, and support for parallel execution in a time-triggered operating system—and thus reflects the breadth of the real-time systems community. I'm convinced that the diverse mix of foundational as well as applied topics will provide for stimulating discussions and encourage lively interactions at the poster session.

It is my hope that the WiP track and the poster session will be interesting to and enjoyable for presenters and the audience alike, and I invite you to join me in taking advantage of this excellent opportunity to learn, to discuss, and to network.

**Björn B. Brandenburg** Max Planck Institute for Software Systems Kaiserslautern, Germany RTAS 2014 WiP Chair

# **RTAS 2014 Work-in-Progress Technical Program Committee**

Andrea Bastoni, SYSGO AG, Germany Marko Bertogna, University of Modena, Italy Bernard Blackham, NVIDIA Corp., UK Aaron Block, Austin College, USA Tommaso Cucinotta, Bell Laboratories Alcatel-Lucent, Ireland Wanja Hofer, Brose Fahrzeugteile GmbH & Co. KG, Germany Cong Liu, The University of Texas at Dallas, USA Alex Mills, Indiana University at Bloomington, USA Harini Ramaprasad, Southern Illinois University Carbondale, USA Michael Roitzsch, Technische Universität Dresden, Germany

# **Technical Program**

| A hybrid system approach to air data estimation in unmanned aerial vehicles<br>Mohammad Shaqura and Christian Claudel                                                         | 1             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| A Refined Approach for Stochastic Timing Analysis<br>Nathan C. Cox, Darius G. Luchian, Thomas E. Herschede, and Christopher A. Healy                                          | 3             |

| Thread Migration for Mixed-Criticality Systems<br>Alexander Zuepke                                                                                                            | 5             |

| What if we would degrade LO tasks in mixed-criticality systems?<br>Marcus Völp                                                                                                | 7             |

| Synchronous Execution of a Parallelised Interrupt Handler<br>Christian Bradatsch, Florian Kluge, and Theo Ungerer                                                             | 9             |

| On the Schedulability of P-FRP Tasks<br>Yu Jiang, Xingliang Zou, and Albert M. K. Cheng                                                                                       | 11            |

| Concurrent soft-real-time execution on GPUs<br>Kiriti Nagesh Gowda and Harini Ramaprasad                                                                                      | 13            |

| Scheduling Hard Real-Time Self-Suspending Tasks In Multiprocessor Systems<br>Maolin Yang, Hang Lei, Yong Liao, and Furkan Rabee                                               | 15            |

| Mapping Real-Time Tasks onto Many-Core Systems considering Message Flows<br>Matthias Becker, Kristian Sandström, Moris Behnam, and Thomas Nolte                               | 17            |

| Comparison of Heuristics and Linear Programming Formulations for Scheduling of In-Tree T<br>Thomas Kothmayr, Jakob Hirscheider, Alfons Kemper, Andreas Scholz, and Jörg Heuer | asksets<br>19 |

| Mathematical Considerations of Linear Real-Time Logic Verification<br>Stefan Andrei, Albert M. K. Cheng, and Mozahid Haque                                                    | 21            |

| Towards a communication-aware mapping of software components in multi-core embedded n                                                                                         | real-time     |

| systems<br>Hamid Reza Faragardi, Kristian Sandström, Björn Lisper, and Thomas Nolte                                                                                           | 23            |

# A hybrid system approach to air data estimation in unmanned aerial vehicles

Mohammad Shaqura, Mechanical Engineering and Christian Claudel, Electrical Engineering, King Abdullah University of Science and Technology

Abstract—Fixed wing Unmanned Aerial Vehicles (UAVs) are an increasingly common sensing platform, owing to their key advantages: speed, endurance and ability to explore remote areas. While these platforms are highly efficient, they cannot easily be equipped with air data sensors commonly found on their manned counterparts since these sensors are bulky, expensive and reduce the payload capability of the UAV. In consequence, UAV controllers have little information on the actual mode of operation of the wing (normal, stalled, spin) which can cause catastrophic failures when flying in turbulent weather conditions. In this article, we propose a real-time air parameter estimation scheme that can run on commercial, low power autopilots in real-time. The computational method is based on an hybrid decomposition of the modes of operation of the UAV. An implementation on a real UAV is presented, and the efficiency of this method is validated using a hardware in the loop (HIL) simulation.

# I. INTRODUCTION

Unlike their ground or water-based counterparts, Unmanned Aerial Vehicles (UAVs) have the potential to be deployed extremely rapidly for surveillance and monitoring applications. Among all types of UAVs, fixed-wing UAVs are the most fuel efficient and the fastest for a given weight and propulsive power. However, manual or automatic flight of UAVs can be complex, as existing air data probes are too bulky, too expensive and too heavy [2] and are thus restricted on heavier, larger and more expensive UAVs. The lack of air data severely restricts pilot or autopilot actuation, and does not allow the operators of the UAV to explore its full flight domain due to the risk of stalls. Numerous articles have been written on the issue of air data estimation, in particular the work of [4], [3] which is based on classical Extended Kalman Filters and LQR methods. While these methods are very accurate, they typically draw significant computational resources to compute the required matrices. In this article, we propose an hybrid system formulation of the UAV dynamics for this purpose. For each mode, we show that the airspeed, angle of attack and angle of sideslip are given by analytical formulas.

### II. HYBRID SYSTEM MODELING

We use the 6-degrees of freedom (6-DOF) equations of motion to model the dynamics of the UAV as a rigid body.

For compactness, we choose not to write these equations in the present article, though these equations relate inertial measurements (acceleration and angular acceleration) to control inputs and the airflow parameters to be estimated. These relations are non linear in terms of the angle of attack  $\alpha$ , angle of sideslip  $\beta$  and airspeed  $V_a$ .

# **III. ESTIMATION METHOD**

To estimate  $\alpha$ ,  $\beta$  and  $V_a$  in real time, we express the nonlinear model as an hybrid model where the dynamics are linear in terms of angle of attack and angle of sideslip in each mode. An analytical expression of the airspeed is computed offline in terms of measurements and inputs. For mode *i*, the linear 6-DOF system of equations can be written as  $A_i x_i = b$  where A is a  $6 \times 2$  matrix that contains the coefficients of  $\alpha$  and  $\beta$  for mode *i* and b is a  $6 \times 1$  vector contains the measurements, control inputs and linear coefficients of  $\alpha$  and  $\beta$ , which are mode dependents.

$$b = [b1 \ b2 \ b3 \ b4 \ b5 \ b6]^T \tag{1}$$

$$A_i = \begin{bmatrix} C_{D_{\alpha i}} & 0 & C_{L_{\alpha i}} & 0 & C_{m\alpha} & 0\\ C_{D_{\beta i}} & C_{Y_{\beta}} & C_{L_{\beta i}} & C_{l_{\beta}} & 0 & C_{n_{\beta}} \end{bmatrix}^T$$

(2)

The least square solution is computed analytically:

$$\begin{bmatrix} \alpha(V_a) \\ \beta(V_a) \end{bmatrix} = (A^T A)^{-1} A^T b \tag{3}$$

We then substitute back  $\alpha$  and  $\beta$  into the nonlinear dynamical model. The explicit formula of  $V_a$  is computed by minimizing the difference between the estimated aerodynamical forces and torques and the actual ones in the norm 2 sense:

$$N1 = F_{AX_{est}} - F_X(V_a) - F_{GX} - F_{throttle}$$

$$\tag{4}$$

$$N2 = F_{AY_{est}} - F_Y(V_a) - F_{GY}$$

<sup>(5)</sup>

$$N3 = F_{AZ_{est}} - F_{GZ} \tag{6}$$

$$N4 - T_{AY} - T_Y(V) \tag{7}$$

$$N4 = T_{AX_{est}} - T_X(V_a)$$

(7)

$$N5 = T_{AY} - T_Y(V_a) - T_Y, ...,$$

(8)

$$N6 = T_{AZ_{est}} - T_Z(V_a)$$

$$(9)$$

$$N(V_a) = (N1^2 + N2^2 + N3^2 + N4^2 + N5^2 + N6^2)(V_a)$$

(10)

$$V_{analytic} = \arg\min_{V} N(V_a) \tag{11}$$

In the present case, the minimization problem yields an analytic solution, which is a function of the inertial measurements, inputs (from the aileron, elevator and throttle) as well as aerodynamic model parameters.

M. Shaqura is a PhD student, Department of Mechanical Engineering, KAUST, 23955-6900 Saudi Arabia. Email: mohammad.shaqura@kaust.edu.sa. Corresponding author

C. Claudel is an Assistant Professor, Department of Electrical Engineering, KAUST, 23955-6900, Saudi Arabia

$$V_{analytic} = f(ax, ay, az, p, q, r, \dot{p}, \dot{q}, \dot{r}, \Delta A, \Delta E,$$

$$throttle, C_{D_{\alpha i}}, C_{D_{\beta i}}, C_{L_{\alpha i}}, C_{L_{\beta i}})$$

(12)

We thus compute the estimated airspeed, angle of attack and sideslip angle for all possible modes (this boils down to applying a  $2 \times 6$  matrix on a vector, and to computing a function of the parameters. Obviously, since each mode *i* yields a different value for the estimated airspeed, angle of attack and angle of sideslip, we identify the mode in which the UAV flies by computing the residuals in the norm 2 sense between the original nonlinear model (in which we apply the estimated values of airspeed, angle of attack and sideslip) and the measurements, then minimizing these residuals.

# **IV. IMPLEMENTATION**

# A. System

The system consists of an RC C-17 Globemaster aircraft [1] equipped with an Ardupilot Mega (APM) v2.6 microcontroller and a number of sensors including barometer, magnetometer, GPS, inertial measurement unit (IMU) and an ultrasound ground proximity sensor. The firmware used in APM is Arduplane, which is an open source code for flight management. The onboard processing is done by the APM processor itself, an Atmel ATMEGA 2560 8-bit chip with 256KB flash memory and a maximum operating frequency of 16 MHz. Given the relatively low computational power of this platform (which also handles a large number of processes related to guidance and attitude estimation), we want to validate that the estimation of  $V_a$ ,  $\alpha$  and  $\beta$  can be performed in real-time.

# B. Simulated computational performance

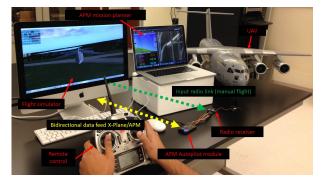

To validate this approach, we use *Hardware-In-The-Loop* (HIL) to test the code execution when the APM microcontroller is interfaced with a commercial flight simulator. We choose the flight simulator X-Plane, and create a UAV matching the specifications of our current UAV, using both computer assisted design and computational fluid mechanics software. We break down the dynamics of the UAV into 15 different modes. The estimation function is implemented as part of the Arduplane code in the 50 Hz loop. We choose this very fast update rate (compared to the typical dynamics of the UAV) since more advanced mode selection schemes will be used in the future. The interface between the APM and X-Plane is done using a customized version of the APM Mission Planner (open source software). The complete setup is illustrated in Figure 1.

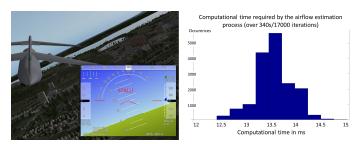

To validate this approach, we used manual flight mode to voluntarily place the UAV in an aerodynamic stall. Aerodynamic stalls occur whenever the angle of attack  $\alpha$  exceeds a threshold (for our UAV: 12°) that is a function of the wing shape and size. As can be seen from figure 2, the estimation process run on the APM detects this event easily. The estimate of the angle of attach for this case was 16°, which can be

Fig. 1. Hardware in the loop simulation setup

Fig. 2. Left: aerodynamic stall detection during a manual HIL flight test. Right: Distribution of the measured computational times of the air data estimation process (running at 50Hz)

confirmed independently by computing the difference between the pitch angle (about  $15^{\circ}$ ) and the angle of climb (about  $0^{\circ}$ ).

# V. CONCLUSION AND FUTURE WORK

In this article, we presented a computational method for air data estimation in Unmanned Aerial Vehicles (UAVs), that can run on the low-power hardware that is typically used on low-cost Micro Air Vehicles (MAVs). This method is based on a hybrid representation of the dynamical model of the UAV, and consists in computing a set of explicit functions of the inertial measurements and input variables, which is very fast. Estimating these airflow parameters in real time is very important in practice to detect stalls (which is a leading cause of crashes, and which is not considered in most UAV autopilots (including the APM) because of the lack of angle of attack sensors), and to detect airspeed sensor faults. Future work will deal with enhanced mode-selection methods based for instance on compressed sensing or on machine learning, taking into account the dynamics of the evolution of the estimated values and residuals.

- M. Abdelkader, M. Shaqura, C.G. Claudel, and W. Gueaieb. A UAV based system for real time flash flood monitoring in desert environments using Lagrangian microsensors. In *ICUAS*, 2013, pages 25–34, 2013.

- [2] M. Ghommem V. Calo C. Claudel. Micro cantilever flow sensor for small aircrafts. SAGE Journal on Vibration and Control, 2013. doi: 10.1177/1077546313505636.

- [3] M.Z. Fekri and M. Mobed. Angle of attack estimation and aircraft controller design using lqr methods. In *Electrical and Computer Engineering*, 2005. Canadian Conference on, pages 2253–2256, May 2005.

- [4] F Adhika Pradipta Lie and Demoz Gebre-Egziabher. Synthetic air data system. *Journal of Aircraft*, 50(4):1234–1249, 2013.

# A Refined Approach for Stochastic Timing Analysis

Nathan C. Cox, Darius G. Luchian, Thomas E. Herschede, Christopher A. Healy Department of Computer Science Furman University Greenville, South Carolina, USA

Abstract—In real-time scheduling, the worst-case execution time (WCET) of a task needs to be known in advance. However, the actual WCET of a task is unlikely to occur in practice. Therefore, scheduling for a soft real-time system can make use of execution times that have a finite probability of being exceeded. As a result, it is desirable to statically compute a program's execution time distribution, rather than just a single number representing an extreme value. In this short paper, we describe ongoing work to produce accurate execution time distributions.

Keywords—WCET analysis, probabilistic timing analysis, scheduling, control-flow analysis

# I. INTRODUCTION

In order to support real-time scheduling, it is necessary to statically predict the worst-case execution time of each scheduled task. Considerable research has been conducted in static WCET analysis [11]. The purpose of such analysis is to guarantee that all deadlines will be met. By contrast, a soft-real time system is one in which an occasional deadline miss degrades performance but is tolerated [7]. The motivation for our present work is that the predicted WCET may be unrealistically high. For soft-real time systems, we may instead want to pursue, say, the 99<sup>th</sup> percentile of the execution time probability distribution. Our aim is to generate the distribution of execution times statically.

Our approach to stochastic execution time looks at the whole distribution, rather than the execution time with a small probability, e.g.  $10^{-12}$ , of being exceeded [5] [2]. Keim et al. introduced an algorithm to statically produce the stochastic timing analysis of a single loop [6]. This approach reduced the problem to using repeated applications of a binomial probability distribution throughout. The approach combined paths in pairs, and results for code having more than two paths were not very accurate. Our motivation was to improve upon this approach and to be able to tackle a wider class of benchmarks.

# II. APPROACH

Our approach follows two directions. One is to gather a time distribution estimate from the timing analyzer, and the other is to glean a corresponding time distribution based on observed execution times. The following is a high-level outline of our approach.

| Compute estimated time distribution:<br>- A compiler produces ARM assembly code. |

|----------------------------------------------------------------------------------|

| - RALPHO produces control-flow information.                                      |

| <ul> <li>Timing analyzer generates distribution.</li> </ul>                      |

| Compute observed time distribution:                                              |

| - A compiler produces ARM executable code.                                       |

| - Run the benchmark repeatedly to gather                                         |

| observed time distribution.                                                      |

| Compare the two distributions, using                                             |

| statistical and integral tests.                                                  |

This methodology relies on three pieces of software. First is an off-the-shelf compiler such as gcc, which can produce assembly and executable code. The other two software tools are our own analysis suite. We modified two existing analysis tools. The assembly code is fed into a revised version of RALPHO [3], in order to produce a control-flow file. This control-flow information is input into a modified timing analyzer [8] to give us the execution time distributions. The modifications to RALPHO are beyond the scope of this paper.

# A. Static calculation

The timing analyzer computes the probability that each path is selected during a loop iteration. This is based on the branch instructions that are encountered in each path. Next, we enumerate the cases of selecting each path for all the iterations of the loop. Note that we are only interested in the number of times that each path is taken, not the sequence in which they occur. This assumption simplifies the analysis.

The approach suggested by [6] works well for two paths, but in our experimentation we found it to be inaccurate for more than two paths. Therefore, we decided to modify the algorithm to use multinomial probabilities [9], instead of repeated applications of the binomial probability. To avoid a combinatorial explosion, we restrict our algorithm to handle up to eight paths. If a loop has more than eight paths, then only the eight most likely taken paths are considered.

Our algorithm computes an execution time distribution for every loop and function in the program. Then, it computes the distribution for the entire program, using the convolution technique of [1]. This step is taken when we need to combine two or more loops, or when a loop or function is nested inside another loop or function. Essentially, the technique is to take the Cartesian product of two distributions, and then re-sort the result so that it has N buckets instead of  $N^2$ .

This work was supported in part by grants from the Furman Advantage and Francis M. Hipp Research Fellowship and the Howard Hughes Medical Institute.

# B. Comparing with Dynamic Calculation

We consider three possible metrics to evaluate the accuracy of the timing analyzer's stochastic distribution versus the observed one. First, we compare the means and standard deviations of the two distributions. Second, we compare the top quantile of each distribution. This is analogous to the usual way of comparing statically predicted versus observed WCETs. This metric also highlights how much lower a likely WCET is compared to its guaranteed WCET.

A third metric is an integral test. It seeks to capture the differences between the probability curves throughout their domain  $0 \le x \le 1$ . The estimated and observed functions (est(x) and obs(x), respectively) are normalized so that the integrals of each function are equal to 1. This is done so that we can allow for a varying number of trials performed when computing obs(x). Then the error can be defined as:

$$e = \frac{1}{2} \int_0^1 |obs(x) - est(x)| \, dx \tag{1}$$

# III. EXPERIMENTAL EVALUATION

We tested our approach on six benchmarks, each having up to five loops. The loops had between two and seven execution paths, inclusive. The code was taken from established set of benchmarks used in WCET analysis [4] [11].

| Test<br>case | Observed<br>mean | Estimated<br>mean | Observed<br>99 %ile | Estimated<br>99 %ile |

|--------------|------------------|-------------------|---------------------|----------------------|

| A*           | 0.77 W           | 0.74 W            | 0.86 W              | 0.97 W               |

| А            | 0.77 W           | 0.76 W            | 0.86 W              | 0.87 W               |

| В            | 0.37 W           | 0.36 W            | 0.49 W              | 0.49 W               |

| С            | 0.71 W           | 0.86 W            | 0.81 W              | 0.88 W               |

| D            | 0.90 W           | 0.88 W            | 0.94 W              | 0.92 W               |

| Е            | 0.90 W           | 0.89 W            | 0.94 W              | 0.90 W               |

| F            | 0.93 W           | 0.90 W            | 0.94 W              | 0.92 W               |

| Avg.         | 0.76 W           | 0.78 W            | 0.93 W              | 0.83 W               |

TABLE I.

RESULTS OF EXPERIMENTS

These results show that the predicted execution time distribution was often very close to the observed distribution. In each case, W represents the predicted WCET of the benchmark. To normalize the results, the second through fifth columns express the execution time as a factor of W. Benchmark A\* is the same as A, and is presented here to compare previous work with ours. The A\* row refers to the result reported by [6]. This benchmark features a loop with seven paths and is now much more accurately predicted, as a result of using multinomial rather than binomial probabilities.

Considering the absolute value of the error of the means, the predicted mean was within 4 percentage points of the observed mean of the execution times. The absolute value of the error in the 99<sup>th</sup> percentile statistics was less than 3 percentage points. For sake of brevity, results of the standard deviation comparison and integral test are not shown.

# IV. ONGOING WORK

Our static analysis tool can generate a statistical distribution of execution times of whole benchmarks. The analysis can handle multiple paths, nested or consecutive loops, as well as the nesting of function calls and/or loops.

We are currently working on improving the accuracy of our stochastic predictions, and expanding the class of programs that we can analyze. For example, we are addressing the problem of individual branch probabilities, to determine which branches govern loop control. We are also modifying RALPHO so that it can accurately compute loop iterations for more complex loop nests.

We also plan to investigate probabilistic runs, i.e. the problem of being temporarily lucky or unlucky in the execution time [9]. This concept has recently been studied elsewhere in the context of predicting performance in the presence of random errors and bursts of random errors in a system [10].

# ACKNOWLEDGMENT

The authors would like to thank Zach Hall and Joey Iannetta for their assistance with RALPHO. Kory Kraft helped to implement the core of the timing analysis algorithm.

### References

- G. Bernat, A. Colin, S. Petters, "WCET analysis of probabilistic hard real-time systems," IEEE Real-Time Systems Symposium, December 2002, pp. 279-288.

- [2] R. Davis, L. Santinelli, S. Altmeyer, C. Maiza, L. Cucu-Grosjean, "Analysis of probabilistic cache related pre-emption delays," Euromicro Conferences on Real-Time Systems, July 2013, pp. 168-179.

- [3] J. Estep, Design and Implementation of the Retargetable Assembly-Level Program Hierarchical Organizer, senior thesis, Furman University, 2003.

- [4] J. Gustafsson, B. Lisper, A. Betts, A. Ermedahl, "The Malardalen WCET benchmarks: past, present and future," International workshop on worst-case execution time analysis, July 2010, pp. 137-147.

- [5] J. Hansen, S. Hissam, G. Moreno, "Statistical-based WCET estimation and validation," International workshop on worst-case execution time analysis, June 2009, pp. 129-133.

- [6] P. Keim, A. Noyes, A. Ferguson, J. Neal, C. Healy, "Extending the path analysis technique to obtain a soft WCET," International workshop on worst-case execution time analysis, June 2009, pp. 134-142.

- [7] P. Laplante, Real-Time Systems Design and Analysis, Wiley-IEEE Press, 2004.

- [8] S. Mohan, F. Mueller, W. Hawkins, M. Root, C. Healy, D. Whalley, "Parametric timing analysis and its applications to DVS," IEEE Trans. Embed. Compt. Syst., December 2010.

- [9] S. Ross, A first course in probability, New York: Macmillan, 3<sup>rd</sup> edition, 1988.

- [10] M. Short, J. Proenza, "Towards efficient probabilistic scheduling guarantees for real-time systems subject to random errors and random bursts of errors," Euromicro Conference on Real-Time Systems, July 2013, pp. 259-268.

- [11] R. Wilhelm et al., "The worst-case execution time problem overview of methods and survey of tools," ACM Trans. Embed. Comput. Syst. 7(3):1-53, 2008.

# Thread Migration for Mixed-Criticality Systems

# Alexander Zuepke RheinMain University of Applied Sciences, Wiesbaden, Germany Email: alexander.zuepke@hs-rm.de

# **II.** System Architecture

Abstract—This work-in-progress paper presents a thread migrating operating system concept for mixed-criticality systems on multi-core platforms. Thread migration provides fast context switching between isolated software components which handle shared resources. Combined with criticality inheritance protocols and a multi-policy scheduler, the described operating system concept aims to meet the level of determinism and analysability which is required for safety-critical applications.

# I. INTRODUCTION

With *Cyber Phyiscal Systems* and the *Internet of Things*, mixed-criticality systems have become a reality in the embedded computing world. Combined with the recent availability of multi-processor systems, it imposes a new challenge on operating systems when different functional units are combined in a single computer system. Similarily, regulatory standards like ISO 26262 require *freedom of interference* between these independent functional units [1]. On the other hand, tight integration of today's hardware technology results in problematic sharing of computational resources like caches and memory bandwidth, and functional resources like I/O devices and buses. An operating system for such scenarios should therefore help to make the side effects of resource sharing *predictable* and enforce the required level of *determinism*.

From a real-time perspective, this means that applications of different *criticality levels* (in the sense of importance to a device's overall function and cost of malfunction) need to be scheduled concurrently. It also requires that access to shared resources and any resulting priority inversion problems need to be solved in a bounded worst-case execution time (WCET) to guarantee that deadlines are met. From a safety perspective, a high degree of separation between different application components and shared components is necessary to guarantee the required freedom of interference and fault isolation. State of the art techniques place applications, drivers, and services into separate address spaces, protected by means of the processor's memory management unit (MMU) [2] [3].

However, while decomposition of a system's components into multiple address spaces helps to fulfill the safety requirements, it entails overhead due to the cost of additional context switches. Therefore, operating system support for mixed criticality systems should include:

- isolation of components in separate address spaces,

- fast context switches between isolated components,

- bounded WCET of all internal operations of the kernel,

- solving of priority inversion problems on shared resources,

- concurrent scheduling of threads of different criticality.

This paper briefly presents the design principles of the WINGERT operating system, which addresses the goals discussed above. Its overall architecure is shown in section II, the benefits of thread migration is described in III, scheduling in IV, resource sharing in V, and related work in VI. We conclude and give an overview of future work in section VII.

The WINGERT OS is built upon a small kernel running in the CPU's privileged mode and a hierarchically structured set of isolated address spaces (tasks) of different criticality in user mode, which comprise applications or services like shared drivers. Following the design principle of a small trusted computing base, critical application tasks only depend on the required subset of tasks providing shared services for them. Communication between tasks is implemented by remote procedure calls (RPCs), which are described in detail in the following section. Starting from the application tasks as the leaves of the task tree, the hierarchy of depending tasks down to the kernel as the root node never decreases in the criticality level. This implies that applications can trust the tasks down in the chain.

Further, all system resources like memory, I/O and time budgets are statically assigned to the tasks at startup. This *resource partitioning* approach eliminates the later need to transfer system resources or access permissions via task communication at runtime, keeping the RPC implementation in the kernel fast and simple.

Each task manages its capabilities in its own name space. Capabilities address the user and kernel parts of threads, interrupts, child tasks, child address spaces, and communication channel endpoints. Memory is addressed differently by its implicit virtual address in the task's page tables. Additionally, tasks can freely repurpose their assigned amount of page-sized *kernel memory* to page tables for dynamically created memory mappings or in-kernel stacks for threads. This degree of freedom allows for example a para-virtualized Linux task to reconfigure itself for different use cases at runtime, without violating the static partitioning approach.

# III. THREAD MIGRATION

The main difference of WINGERT compared to other micro kernels like L4 lies in its low-level abstraction model named *body and soul* instead of threads as the basic entities of execution. The *soul* is a scheduling entity with priority, deadline, and a kernel stack. It migrates synchronously between different *bodies*, which comprise of an entry point and dedicated stack in user space. The invocation of a new body resembles an RPC call to the same or a remote address space, while keeping the calling soul to have a unique entity to control the execution flow and to reduce context switching overhead in the kernel.

For asynchronous communication and decoupling of potentially blocking calls, the kernel provides *fork-join* operations: a soul forks and instructs its forked sibling to issue a synchronous RPC. With a technique named *lazy forking*, the kernel follows the forked path using the original soul first and performs the real fork operation when a blocking point is encountered. Assuming there is no blocking point, the forked one returns the result and joins gracefully without any overhead.

# IV. SCHEDULING

The practical challenge of mixed-criticality scheduling lies in reclaiming scheduling reservations of higher critical tasks at run time caused by their overly pessimistic WCET analysis. Inspired by  $MC^2$  [4], the kernel scheduler provides multiple scheduling policies for different levels of criticality. In descending order of criticality, these are:

- 1) P-FP: partitioned fixed-priority scheduling

- 2) P-EDF: partitioned earliest deadline first scheduling

- 3) G-FP: global fixed-priority scheduling

- 4) G-EDF: global earliest deadline first scheduling

- 5) BE: best effort scheduling for non-real-time applications

- 6) IDLE: scheduling of idle threads of the lowest level

All scheduling policies are mapped into the same priority space, but have disjoined priority ranges and different queueing policies (FIFO or deadline ordered). The highest priority level ready queues are kept exclusive per processor to ensure partitioned scheduling, the lower levels share a single set of ready queues. The dispatcher picks the highest eligible thread for scheduling on its CPU. Supporting other scheduling policies, like the ones used by Linux, is not the responsibility of the OS scheduler. On top of this system, a para-virtualized Linux implementation would use its built-in scheduler and dispatch its processes by thread migration.

# V. RESOURCE SHARING

WINGERT provides two different mechanisms for synchronization and resource sharing: thread migration across tasks; and mutexes and condition variables shared by threads in the same task. The latter use *Deterministic Futexes* described in [5] as the underlying kernel mechanism. The implementation enters the kernel only on contention and uses atomic operations on variables in user space in the fast path.

As bodies have a single user space stack only and therefore do not support multiple souls inside, migrating souls have to wait when a body is already occupied. With an extension to let souls *wait* outside the body and let them stay there until they are *signalled* again by the body, the body effectively becomes a *Monitor* [6].

On contention, both bodies and futexes need to properly solve priority inversions problems. The standard *priority inheritance protocol* (PIP) [7] solves this issue for the class of highest criticality P-FP scheduling. Additionally, the protocol covers P-EDF by prefering earlier deadlines on priority ties. Finally, with *migratory priority inheritance* [8], the scheduler migrates preempted threads across CPUs and solves priority inversions in global scheduling scenarios. With these extensions for mixed-criticality scheduling, the described protocol effectively becomes a *criticality inheritance protocol*.

# VI. RELATED WORK

WINGERT has in common with micro kernels like L4 [9] a similar overall system structure of decomposed software components in isolated address spaces and the use of a synchronous context switch mechanism as a means of communication [2]. However, our approach is more specific to the mixed-criticality use case than the policy-free approach in L4.

Thread migration was previously used in [10], [11], and [12]. Compared to COMPOSITE, which uses thread migration and solves contention on user stacks with PIP and PCP (priority ceiling protocol) [3], the presented approach scales to multi-processor platforms.

# VII. CONCLUSION AND FUTURE WORK

This paper presented the WINGERT operating system, which aims to exploit thread migration for real-time systems. Using thread migration for strictly hierarchical system designs such as mixed-criticality systems seems to be a good trade-off between software component isolation for safety reasons on the one hand and fast performance on the other hand, while at the same time reducing the number of possibly misbehaving actors and keeping the overall system complexity low.

In future work, we plan to evaluate the system performance and provide an in-depth analysis of the presented criticality inheritance protocol, with a special focus on an implementation with a bounded WCET.

### References

- [1] ISO 26262, "Road vehicles Functional safety," 2011.

- [2] J. Liedtke, "On μ-Kernel Construction," in SOSP, 1995, pp. 237–250.

- [3] Q. Wang, J. Song, and G. Parmer, "Execution Stack Management for Hard Real-Time Computation in a Component-Based OS," in *RTSS*, 2011, pp. 78–89.

- [4] J. L. Herman, C. J. Kenna, M. S. Mollison, J. H. Anderson, and D. M. Johnson, "RTOS Support for Multicore Mixed-Criticality Systems," in *RTAS*, 2012, pp. 197–208.

- [5] A. Zuepke, "Deterministic Fast User Space Synchronisation," in OS-PERT Workshop, 2013.

- [6] C. A. R. Hoare, "Monitors: An Operating System Structuring Concept," Commun. ACM, vol. 17, no. 10, pp. 549–557, Oct. 1974.

- [7] L. Sha, R. Rajkumar, and J. P. Lehoczky, "Priority Inheritance Protocols: An Approach to Real-Time Synchronization," *IEEE Trans. Computers*, vol. 39, no. 9, pp. 1175–1185, 1990.

- [8] B. B. Brandenburg and A. Bastoni, "The case for migratory priority inheritance in linux: Bounded priority inversions on multiprocessors," in *Fourteenth Real-Time Linux Workshop*, 2012.

- [9] K. Elphinstone and G. Heiser, "From L3 to seL4 What Have We Learnt in 20 Years of L4 Microkernels?" in SOSP, 2013, pp. 133–150.

- [10] B. Ford and J. Lepreau, "Evolving Mach 3.0 to A Migrating Thread Model," in USENIX Winter Conference, 1994, pp. 97–114.

- [11] G. A. Parmer, "Composite: A Component-based Operating System for Predictable and Dependable Computing," Ph.D. dissertation, Boston, MA, USA, 2010.

- [12] E. Gabber, C. Small, J. Bruno, J. Brustoloni, and A. Silberschatz, "The Pebble Component-based Operating System," in USENIX ATC, 1999.

# What if we would degrade LO tasks in mixed-criticality systems?

Marcus Völp School of Computer Science, Logical Systems Lab Carnegie Mellon University Pittsburgh, PA, USA mvoelp@cs.cmu.edu

# I. INTRODUCTION

Mixed-criticality (MC) systems [1] allow tasks of different importance (or criticality) to be consolidated into a single system. Consolidation facilitates resource sharing (even across criticality levels) and hence bears the potential to reduce the overall amount of resources needed. However, there is a common misconception that recurs in literature about Vestal's model: the false believe that low criticality tasks are degraded to soft real-time or even best effort tasks. In this work, we not only wish to clarify this misconception but also ask ourselves what would happen if we degrade LO tasks. Revisiting Quality Assuring Scheduling (QAS) [2], [3], our goals are stochastic guarantees for LO completion in addition to and replacing the hard MC guarantees if LO tasks are soft real-time. In this WIP report, we focus on properties of dropped LO tasks (while keeping hard MC guarantees) such as: "What is the likelihood of lower criticality jobs being dropped because higher criticality jobs exceed their low WCET estimates?", "What is the likelihood of dropped jobs to still make their deadline?", and "What is the expected time / Q-percentile for dropped jobs to catch up with their execution?". Part of our future work will be to extend these guarantees and to develop MC schedulers for a combination of hard and soft real-time tasks. Notice though, that the assumptions in this report still limit the applicability of our results. We indicate how we plan to relax them in the future. Most notably, we assume that jobs arrive in their synchronous arrival sequence and that executiontime distributions are known. The latter we plan to replace with confidence of WCET estimates.

### II. MIXED-CRITICALITY SCHEDULING

Let  $\mathcal{T}$  be a set of sporadic tasks. As usual, we characterize  $\tau_i \in \mathcal{T}$  by tuples  $(l_i, D_i, T_i, C_i)$  where  $l_i$  is a criticality level in the ordered set of criticality levels  $\mathcal{L}$  (e.g.,  $\mathcal{L} = \{LO, HI\}$ with LO < HI),  $D_i \leq T_i$  is the relative deadline and  $T_i$ the minimal interrelease time. We subject tasks to execution time analyses suitable for the individual levels. The result is a vector of increasingly more pessimistic WCET estimates  $C_i(l)$ . The set  $\mathcal{L}$  and the requirements for considering an analysis suitable may be drawn from evaluation criteria such as DO-178C [4] but other metrics are also conceivable. We assume the system enforces budgets  $C_i(l_i)$  and subject  $\tau_i$  only to the WCET analyses for all  $l \leq l_i$ . The feasibility criteria and hence the guarantee given to all admitted tasks is:

Definition 1 (Feasibility): The set  $\mathcal{T}$  is feasible if every job  $J_l = \tau_{i,j}$  receives  $C_i(l_i)$  time in between its release time  $r_l$  and its absolute deadline  $r_l + D_i$  provided no job  $J_h$  of a higher criticality task with  $l_h > l_i$  exceeds its low WCET estimate  $C_h(l_i)$ .

There are two important points to notice:

- 1) If no higher-criticality job  $J_h$  exceeds its low estimate  $C_h(l_l)$ , lower criticality jobs  $J_l$  receive the same hard real-time guarantees as in a classical system. That is, provided all WCET estimates are safe, they receive sufficient time to complete before their deadlines; and

- 2) No guarantee is given to these jobs once a higher criticality job exceeds its low WCET estimate.

Notice also that dropped jobs merely loose their real-time guarantees (and possibly their high prioritized budget). There is no necessity to terminate these jobs. The question about low-criticality guarantees now boils down to whether WCET estimates are safe or whether in some rare situations the actual execution time may exceed these estimates. Either way, MC schedulers convey no guarantee about the subset of deadlines low criticality tasks meet, which is essential for soft real-time.

# III. QUALITY ASSURING SCHEDULING

QAS [2] offers stochastic guarantees for imprecise computations [5] where jobs are composed of mandatory parts, which must execute to completion, and optional parts, which improve the final result. For the first, a safe WCET estimate  $(\mathbf{P}[X_i \leq C_i] = 1)$  is anticipated whereas for the latter QAS assigns budgets  $b_i^k$  resulting from requested  $Q_i$ -percentiles of the execution time distribution  $(\mathbf{P}[X_i \leq b_i^k] = Q_i)$ . Here and in the following  $X_i$  and  $Y_i^k$  denote non-negative random variables capturing actual execution times and  $\mathbf{P}[X_i \leq c]$ stands for the probability that  $X_i \leq c$ . QAS aborts parts at their assigned budgets but considers the actual execution time distribution to determine the likelihood of lower prioritized jobs meeting their deadlines. The  $k^{th}$  optional part  $o_i^k$  is executed (possibly at a different priority) only if all prior optional parts completed in time. For the special case where tasks shares a common release time r and deadline D, the job  $J_i$  completes  $o_i^k$  with probability p if

$$\begin{split} \mathbf{P}[Y_i^k < b_i^k \wedge (\sum_{j \in \mathbf{hp}_i} X_j + \sum_l \min{(Y_j^l, b_j^l)} + X_i + \sum_{m \le k} \min{(Y_i^m, b_i^m)}) < D] = p \end{split}$$

# IV. OPTIONAL PARTS MEET MIXED CRITICALITY

Our goal is to translate MC scheduling into QAS to (1) reuse the feasibility and abortion results and (2) devise new algorithms to convey stochastic guarantees for LO jobs.

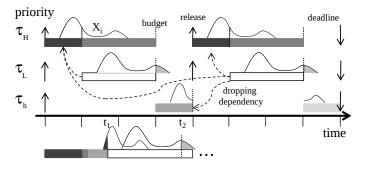

Fig. 1. Mixed-criticality schedule with execution-time distributions  $X_i$  and optional-part dependencies (dashed lines) for the tasks  $\tau_H = (HI, 4, 4, (1, 3)), \tau_L = (LO, 4, 4, (2, -))$  and  $\tau_h = (HI, 8, 8, (1, 2))$  with  $J_1 = \tau_{H,1}, J_2 = \tau_{L,1}, J_3 = \tau_{h,1}, J_4 = \tau_{H,2}, J_5 = \tau_{L,2}$ . There is still a chance to complete  $J_2$  after dropping it, even if  $J_2$  exceeds its initial budget.

a) Likelihood to drop low criticality jobs: Fig. 1 shows an example of a standard (i.e., not QAS) adaptive MC algorithm. The algorithm is adaptive in that  $\tau_L$  must be dropped (i.e., the priority of  $\tau_L$  must change) to guarantee the completion of the two HI tasks in case  $J_1$  exceeds  $C_H(LO)$ . In other words,  $X_1 < C_H(LO)$  must hold for  $J_2$  to not be dropped and in addition  $X_3 < C_h(LO)$  and  $X_4 < C_H(LO)$  to start executing  $J_5$ . But these are exactly the conditions for the execution of optional parts. By regarding the LO parts of HI jobs whose criticality decision point is before the worst-case response time  $R_k^{LO}$  of a job  $J_k$  as preceding optional parts of this job, QAS gives us the likelihood of this job being dropped as:

$$1 - \prod_{\tau_i \in T \mid R_i^{LO} \le R_k^{LO}} \mathbf{P}[X_i < C_i(LO)]$$

(1)

where  $R_i^{LO} = C_i(LO) + \sum_{\tau_j \in \mathbf{hp}(i)} \left\lceil \frac{R_i}{T_j} \right\rceil C_j(LO)$  is the worstcase response time of  $J_i$  assuming all higher prioritized job  $J_j$ require no more than  $C_j(LO)$ . Fig. 1 indicates this *dropping dependency* as dashed lines. The criticality decision point of a job  $J_k$  is the worst-case response time of its low part. At this point, we know whether  $J_k$  causes LO tasks to be dropped <sup>1</sup>.

b) Likelihood of dropped jobs meeting their deadlines: The bottom part of Fig. 1 shows that it is possible to complete the dropped job  $J_2$  at a priority level where it can no longer defer the execution of  $J_3$ , which could have caused a deadline miss.  $J_2$  completes in time if after  $J_1$  has exceeded  $C_H(LO)$ the combined execution time  $X_1 + X_2 + X_3$  is less than or equal to  $D_L$ .  $J_2$  may even complete if  $C_L(LO)$  is an unsafe WCET estimate, for example if  $J_3$  stops before time  $t_1$  and if additional time is given to  $J_2$  after  $t_2$ . More generally, if a HI job  $J_k$  does not complete, it receives an additional part with  $Y_k = \max(X_k - C_k(LO), 0)$  and the originally scheduled parts of LO jobs  $J_l$  in dropping dependency with  $J_k$  are aborted. Instead of not executing dropped jobs  $J_l$ , we assume they receive a possibly larger budget at a priority level that is sufficiently low to not risk high completion. Priorities in a strictly lower band fulfill this condition, however, we expect to find less pessimistic setups in the future. The important constraint (in particular when considering more than two criticality levels) is to preserve the relative priority ordering of dropped jobs because then MC guarantees extend to the

<sup>1</sup>Notice, there is no need to make this decision earlier because the completion of no high task is at risk. stochastic MC guarantees for dropped jobs. That is, dropped jobs with a higher criticality level than other dropped jobs complete more likely. As a preliminary result, the likelihood that a dropped job  $J_i$  meets its deadline under the condition that  $\pi(J_1) > \ldots > \pi(J_{i-1})$  denotes the priority ordering of higher than  $J_i$  prioritized jobs after jobs have been dropped is  $\mathbf{P}[\max(T_{i-1}, r_i) + X_i < r_i + D_i]$  where  $T_{-1} = T_0 = 0$  and

$$T_{k} = \begin{cases} \max(T_{k-1}, r_{k}) + X_{k} & \text{if } \max(T_{k-1}, r_{k}) + \\ X_{k} < r_{k} + D_{k} & X_{k} < r_{k} + D_{k} \\ \max(T_{k-2}, r_{k} + D_{k}) & \text{otherwise} \end{cases}$$

(2)

c) Time to catch up: Even without the above precaution LO jobs  $J_k = \tau_{l,m}$  may catch up with their execution by exploiting the budgets of the next jobs of their tasks. Notice, the result is late and its value degraded.  $\tau_{l,m}$  catches up after consuming max  $(X_{l,m} - F, 0)$  of  $\tau_{l,m+1}$ 's budget and both  $\tau_{l,m}$  and  $\tau_{l,m+1}$  complete before  $\tau_{l,m+1}$ 's deadline if  $\tau_{l,m+1}$  would complete with its execution-time distribution changed to max  $(X_{l,m} - F, 0) + X_{l,m+1}$  where F is the time that  $\tau_{l,m}$  did run before consuming  $\tau_{l,m+1}$ 's time.

# V. RELATED WORK

To our best knowledge, this is the first attempt to cast MC scheduling into an imprecise computation context. There is of course a large body of work on probabilistic analyses and scheduling of non-MC systems. Alahmad et al. [6] investigate probabilistic execution-behavior models and identify stochastic MC scheduling as an open problem [7]. In contrast to our work, they seek to optimize the feasibility of the MC schedule itself, not only of dropped tasks. Also they do not consider the possibility of unsafe WCET estimates for *LO* jobs.

# VI. CONCLUSIONS

We present first results connecting quality assuring and mixed-criticality scheduling to give stochastic guarantees for dropped jobs<sup>2</sup>.

- S. Vestal, "Preemptive scheduling of multi-criticality systems with varying degrees of execution time assurance," in *Real-Time Systems Symposium*. Tucson, AZ, USA: IEEE, December 2007, pp. 239–243.

- [2] C.-J. Hamann, J. Löser, L. Reuther, S. Schönberg, J. Wolter, and H. Härtig, "Quality Assuring Scheduling - Deploying Stochastic Behavior to Improve Resource Utilization," in 22nd IEEE Real-Time Systems Symposium (RTSS), London, UK, Dec. 2001.

- [3] C.-J. Hamann, L. Reuther, J. Wolter, and H. Härtig, "Quality-assuring scheduling," TU Dresden, Dresden, Germany, Tech. Rep. TUD-FI06-09, December 2006.

- [4] DO-178C: Software Considerations in Airborne Systems and Equipment Certification, RTCA, Dec. 2011.

- [5] J.-Y. Chung, J. W. S. Liu, and K.-J. Lin, "Scheduling periodic jobs that allow imprecise results," *IEEE Transactions on Computers*, vol. 39, no. 9, pp. 1156–1173, Sep. 1990.

- [6] B. Alahmad, S. Gopalakrishnan, L. Santinelli, and L. Cucu-Grosjean, "Probabilities for mixed-criticality problems: Bridging the uncertainty gap," in *Real-Time Systems Symposium - Work in Progress*, Vancouver, Canada, Nov. 2011.

- [7] B. Alahmad and S. Gopalakrishnan, "Can randomness buy clairvoyance? a look into stochastic scheduling of mixed criticality real-time job systems with execution time distributions," in *3rd Int. Real-Time Scheduling Open Problems Seminar (RTSOPS)*, Pisa, Italy, July 2012.

<sup>&</sup>lt;sup>2</sup>This work is partially funded through NSF Grant CNS-0931985 and by the DFG through the cluster of excellence *Center for Advancing Electronics Dresden*.

# Synchronous Execution of a Parallelised Interrupt Handler

Christian Bradatsch, Florian Kluge, Theo Ungerer Department of Computer Science University of Augsburg 86159 Augsburg, Germany {bradatsch,kluge,ungerer}@informatik.uni-augsburg.de

Abstract—Upcoming multicore processors for embedded realtime domains allow the integration of multiple applications and new features in electronic control units. PharOS [1] enables an efficient parallelisation of tasks by executing these in a timetriggered manner on a multicore processor. Many processes especially in the automotive domain are event triggered. PharOS allows to define event triggered tasks with short deadlines and hence only a low complexity. We also see the need for more complex event-triggered tasks that need to be parallelised. Still, we want to profit from the benefits of the time-triggered execution model. We propose a method to execute a parallelised interrupt handler synchronously within the PharOS execution model on a network-on-chip based manycore processor.

# I. INTRODUCTION

Multicore processors are entering the domain of safetycritical real-time systems. This enables the integration of new features and of more complex control algorithms, e.g. in automotive electronic control units. With PharOS [1], an operating system was proposed to enable the use of multicore processors in safety-critical automotive systems. With increasing core numbers, those efforts have to go hand in hand with an efficient parallelisation of applications, thereby still keeping well-known safety properties. The time-triggered execution model used in PharOS enables such a parallelisation for timetriggered tasks. However, we also foresee the need for a parallelisation of event triggered tasks, like more complex crank angle triggered interrupt handlers in an engine management system. While the concept of event triggered tasks is part of PharOS, their parallelisation is not discussed.

Our aim is to execute a parallelised interrupt handler on a manycore processor, where the single cores are linked by an interconnect. In such an architecture, communication between cores takes place in the form of implicit or explicit messages. Depending on source and sink nodes, the messages can have varying worst-case traversal times (WCTTs). A multicast message sent by one core will arrive at different times at the receiver cores. Still, we must ensure that the actual processing of such a message starts at the same time on all cores.

In the following section, we briefly review the properties of the PharOS execution model and discuss their adequacy for the parallelisation of interrupt handlers. Our method for synchronous execution of a parallelised interrupt handler is presented in section III. A first prototype implementation is outlined in section IV. In section V, we give an outlook on future work.

# **II. EXECUTION MODEL**

PharOS is based on the time-triggered execution model of OASIS. OASIS [2] defines an approach for the design of safety-critical systems, e.g. in nuclear power plants. In OASIS, all tasks are executed in a time-triggered manner. Each task  $\omega$  has an associated real-time clock  $H_{\omega}$ . This clock is defined by the time instances at which input and output of the task can occur. Tasks can use an instruction ADV(n) to advance their clock by n instants. A task is then activated again n instants after its last activation. During clock advancement, execution of the calling task is blocked.

For communication between tasks, OASIS defines temporal variables and an asynchronous message passing mechanism. Both mechanisms are coupled to real-time clocks. Sent data is visible at the receiver at predefined time instants. The implementation of these mechanisms ensures that neither senders nor receivers experience blocking times. This model allows to implement concurrent tasks without explicit synchronisation, leading to a less pessimistic WCET analysis as no blocking times through interferences between tasks can occur. Indeed, the only blocking times that can occur are those requested by tasks themselves through the use of the *ADV* instruction.

PharOS [1] extends the OASIS concepts for automotive systems using multicore processors. PharOS partitions a system into time and event triggered domains. Each domain is assigned to dedicated cores. Time-triggered tasks are referred to as *agents* and executed on *computing cores*. In addition, PharOS places event-triggered tasks, called *handlers*, on *control cores*. The control core also processes I/O interrupts. This concept is demonstrated by an example where a handler task monitors a PWM signal for its duty cycle and sends measured data to an agent for further processing.

In our work, we go one step further. Our aim is to parallelise an interrupt handler and benefit from the advantages of the OASIS/PharOS execution model. The need for such an approach arises, if an interrupt handler not only has to read some input data, but also must process the data and set some output within a short deadline. If, furthermore, such an interrupt can occur with widely varying inter-arrival times, it is hard to dislocate processing and output into the time-triggered domain, if possible at all.

# **III. START TIME SYNCHRONIZATION**

The target of the proposed approach is a parallelised and synchronous processing of an IRQ handler. We assume that agents are executed exclusively on computing cores and handlers on control cores accordingly. An I/O interrupt is only triggered at one dedicated control core. On this core, an *initial* handler is executed which does not use the time-triggered execution model. The initial handler sends messages to activate processing of the IRQ by the processing handlers running on other control cores. Thereby, two requirements have to be fulfilled: (1) the latency between the occurrence of the IRQ and the start of the actual processing must be statically boundable and sufficiently low to allow schedulability, and (2) the processing handlers must start execution at the same time such that their implementation can also use the timetriggered execution model of OASIS/PharOS. From the second requirement follows, that an event triggered processing handler must also be able to use the ADV instruction like tasks executed in the time-triggered domain. For the ADV instruction a clock reference point is required. In the time-triggered domain this reference point is the start of the program.

To obtain such a reference point for processing handlers, we extend the messages sent by the initial handler by a future-timestamp. This future-timestamp represents the clock reference point. It is computed from the actual timestamp when entering the initial handler and the WCTT of the messages. Each receiving control core uses an *ADV* instruction to advance to this future-timestamp. Thereafter all cores start their processing handler synchronously at the same time.

To realise this approach, two requirement must be fulfilled by the underlying hardware: (1) A message mechanism must be available which signals an incoming message at receiver side immediately. (2) All cores need a common, fine-granular time base.

# IV. IMPLEMENTATION

We have performed a first prototype implementation of our approach on the manycore simulator of the parMERASA project [3]. The simulator provides a common time base for all cores by hardware, a flexible interrupt system, and a global address space.

Our use case is an engine control application using, amongst other things, an interrupt triggered by certain crank angle positions. The occurrence of this crank angle interrupt varies within a certain range depending on the rotation speed of the crank shaft. The interrupt signal is processed by the initial handler on a dedicated core. The aim is to execute a parallelised version of the crank angle interrupt handler routine. Currently, only one processing handler is executed exclusively on each control core. Due to that circumstances, a control core is actively waiting for an incoming message and thus needs not to be interrupted by a message notification. This simplifies the implementation. After an interrupt is asserted at the dedicated interrupt core, the initial IRQ handler is started. The initial handler requests the actual time base and adds a WCTT offset that was calculated offline. The result is the clock reference point  $t_r$  which is stored at a specific location  $m_t$  in shared memory. Afterwards, the initial handler returns, and the core can also execute a processing handler. Each control core that shall execute a processing handler is spinning on the memory location  $m_t$  until its value changes. It then loads the value  $t_r$  into a register and executes an  $ADV_{abs}(t_r)$  instruction, that advances to an absolute point in time. Thus, a synchronous start of all processing handlers is enabled.

In our case the WCTT of the message is calculated as the sum of the WCET of the store instruction executed by the initial handler and the WCET of the load instruction executed by the processing handlers. Measurements have shown that the deviation of the start time of each handler is up to 50 clock cycles. Additionally, the actual execution of the handlers starts 150-200 cycles after  $t_r$  elapsed. This circumstance is due to the fact that memory accesses to shared as well as private memory are routed through the interconnect of the simulated processor. Thereby, interferences on the interconnect occur and the latency for accesses is quite long. The same effect was also observed when an ADV(n) instruction with the same clock value n was executed on all cores in the time-triggered domain. So the deviations are likely to result because of the underlying hardware.

# V. CONCLUSIONS AND FUTURE WORK

We have presented an extension of the ADV instruction that was introduced in OASIS. This extension,  $ADV_{abs}$ , allows to advance execution to an absolute point in time. Thus, we achieve to synchronously start the threads of a parallelised interrupt handler, and their implementation is able to profit from the time-triggered execution model. In the future, we plan to investigate in two directions. First, we will compare our polling mechanism to messages sent via inter-core interrupts. Second, we will integrate agent and handler tasks on single cores to improve utilization compared to exclusive control cores. The consequences for schedulability of both task types will be analysed.

# ACKNOWLEDGEMENTS

Part of this research has been supported by the EC FP7 project parMERASA under Grant Agreement No. 287519.

- [1] C. Aussaguès, D. Chabrol, V. David, *et al.*, "PharOS, a multicore OS ready for safety-related automotive systems: results and future prospects", in *Embedded Real-Time Software and Systems (ERTS<sup>2</sup>* 2010), Toulouse, France, May 2010.

- [2] C. Aussagués and V. David, "A method and a technique to model and ensure timeliness in safety critical real-time systems", in *Fourth IEEE International Conference on Engineering of Complex Computer Systems (ICECCS '98)*, 1998, pp. 2–12.

- [3] T. Ungerer, C. Bradatsch, M. Gerdes, et al., "parMERASA multicore execution of parallelised hard real-time applications supporting analysability", in *Euromicro Conference on Digital System Design* (DSD), 2013, Los Alamitos, CA, USA: IEEE, Sep. 2013, pp. 363–370.

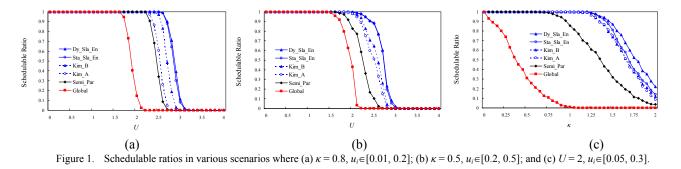

# On the Schedulability of P-FRP Tasks

Yu Jiang<sup>+</sup>

School of Computer Science and Technology Heilongjiang University Harbin, Heilongjiang 150001, China jiangyu@hlju.edu.cn

Abstract—As a variant of Functional Reactive Programming (FRP), priority-based FRP (P-FRP) maintains both type-safety and state-less execution paradigm of FRP, and supports assigning different priorities to different tasks in real-time systems. Since the abort-and-restart execution semantics of P-FRP are different from that of the classical preemptive model, the schedulability analysis for P-FRP is much of difference and difficulty. In this short paper we briefly present our ongoing work about an exact schedulability condition and a response time bound we have newly discovered for scheduling P-FRP tasks.

Keywords—real-time system; schedulability; functional reactive programming (FRP); priority-based FRP; response time analysis; feasibility interval; permissibility interval

# I. INTRODUCTION

# A. Motivations and contributions

Compared with the classical preemptive model [1], the schedulability analysis for *Priority-based Functional Reactive Programming* (P-FRP) [2] is of difficulty because of the abortand-restart feature and scheduling uncertainty of lower priority tasks interfered by higher priority tasks. For a P-FRP *n*-task set, the current schedulability condition [3] is only being sufficient and is utilization-based with the bound 1/n under some restrictions on the task periods, making it less useful as *n* gets larger. If some conditions could be found without this kind of restrictions it would be much better. Furthermore, under the P-FRP model, for a given release pattern such as synchronous, for the computation-based actual response time analysis, a higher performance algorithm is needed, which is also beneficial to the *worst-case response time* (WCRT) study.

In this work-in-progress paper, we present an exact (necessary and sufficient) schedulability condition for P-FRP *n*-tasks with the *rate monotonic* (RM) scheduling, without using the utilization bound.

# B. Backgrounds and related works

Functional Reactive Programming(FRP) [4] is a declarative programming language for the modeling and implementation of safety-critical embedded systems, and is getting widely used in preemptive reactive systems. However, it has no real-time guarantees. To address this limitation, P-FRP has been put forward, which maintains both type-safety and state-less execution paradigm of FRP, and supports assigning different priorities to different tasks in real-time systems.

Different from the classical preemptive model in which tasks can resume execution from the point they were

Xingliang Zou<sup>+</sup>, Albert M. K. Cheng Department of Computer Science University of Houston Houston, TX 77004, USA xzou@uh.edu, cheng@cs.uh.edu

preempted, in P-FRP lower priority tasks will resume in a transactional execution way, i.e., resuming execution from the very beginning, in order to meet the natural requirement of atomic execution of FRP. Therefore, P-FRP is characterized as the abort-and-restart execution semantics.

In their seminal paper, Liu and Layland [1] have shown that, in the classical preemptive model using the RM scheduling for periodic tasks with deadlines equal to periods, a *n*-task set is schedulable if the first instance of each task can meet its deadline when these tasks are released synchronously (at the same time). Based on the processor utilization bound, they also presented a necessary condition of schedulability for periodic tasks using the RM scheduling. For schedulability analysis under the classic preemptive model with a given priority assignment, there are also some other research work such as [5-8]. However, the schedulability tests discovered for the classical preemptive model, using either processor utilization bound or an iterative equation to compute the WCRT then for checking up the schedulability, do not apply directly to the P-FRP model because of the abort-and-restart feature and hence the uncertain response time of the P-FRP.

In [3] the authors put forward a necessary schedulability condition for 2-task sets, and some sufficient schedulability conditions for 2-task sets and *n*-task sets in P-FRP, based on processor utilization and under certain restrictions on periods and release scenarios. In [9] and [10] they further present the Gap-enumeration and idle-period game board algorithms, respectively, for computing the actual response time, and then the schedulability of the task set is determined. However, both algorithms have some slack in performance due to higher search costs or balance-tree maintaining costs [10]. The authors also present in [11] the feasibility of using time Petri nets for schedulability analysis in P-FRP for small task sets. In [12] the authors prove the feasibility interval for *n*-task sets.

# II. BASIC CONCEPTS AND NOTATIONS

In this paper, we consider a P-FRP real-time uniprocessor system with a set of independent, periodic *n* tasks. A task  $\tau_i$ has a (*maximum*) computation time  $C_i > 0$ , an arrival time period  $T_i$ , a relative deadline  $D_i$  equal to its period  $T_i$ , i.e.,  $D_i=T_i>0$ , and a release offset  $O_i \ge 0$  which is the release time of the first instance of the task and is relative to time 0. For later notational convenience we label the tasks so that task  $\tau_i$  is assigned a fixed priority *i*, where *n* is the lowest priority. When using the *RM* scheduling, there will be  $T_1 \le T_2 \le ... \le T_n$ .

For  $1 \le k \le n$ , let  $\Gamma_k = \{\tau_1, \tau_2, ..., \tau_k\} \subseteq \Gamma_n = \{\tau_1, \tau_2, ..., \tau_n\}$ ,  $O_{min}^{(j)} = min_{i=1}^k \{O_i\}$ , and  $O_{max}^{(j)} = max_{i=1}^k \{O_i\}$ .

This work is sponsored in part by the State Scholarship Fund of China under award No. 201308230034, and in part by the US National Science Foundation under award Nos. 0720856 and 1219082.

We use  $LCM_k$  to represent the *least common multiple* (*LCM*) of the periods of the first *k* tasks, i.e.,  $LCM_k=LCM(T_1,T_2,...,T_k)$ ,  $1 \le k \le n$ , and  $LCM_1=T_1$ .

An *absolute time* t (or *time* t) is the time elapsed since the start, which is assumed to be at the absolute time 0, of the realtime system. A *half-closed interval*  $[t_i, t_j)$  represents a time interval such that:  $\forall t \in [t_i, t_i), t_i \leq t < t_i \land t_i \neq t_i$ .

A *feasibility interval* is the time interval [t, t+H) such that if all tasks are schedulable in [t, t+H) then the tasks will also be schedulable in the time interval [0, Z):  $Z \rightarrow \infty$  [12].

We define the *i-permissibility interval* for task  $\tau_i$  as the

time interval  $[t_j, t_k)$  such that the length of the interval, i.e.,  $t_k$ - $t_j$ , is no less than  $C_i$ , and in which no higher priority task is awaiting execution and ready to execute strictly before  $t_j$ . Notice that this concept is different from the *k*-gap in [9] which has not taken the requirement of interval length into account in the definition of the *k*-gap.

Due to space limitation, the execution model is referred to [12]. When considering abort and restore costs, the *computation time*  $C_i$  can be replaced by the *processing time*  $P_i$  for simplicity.

# III. OUR RESULTS

In this section we briefly present our new results on the schedulability condition without using the utilization bound, and a method of computing the WCRT upper bound, for P-FRP *n*-tasks using the *RM* scheduling.

# A. An exact schedulability condition

**Lemma 1.** Considering a schedulable *n*-task set  $\Gamma_n = \{\tau_1, \tau_2, ..., \tau_n\}$  using fixed task priority, with a given release order such that for all  $1 \le j \le n$ ,  $0 \le O_j < T_j$ , then, for each  $1 \le k \le n$ , (1) for any  $t \ge O_{min}^{(k)}$ , the release and executing patterns of  $\Gamma_k = \{\tau_1, \tau_2, ..., \tau_k\} \subseteq \Gamma_n$  in the intervals  $[t+m \cdot LCM_k, t+(m+1) \cdot LCM_k)$  and  $[t+(m+1) \cdot LCM_k, t+(m+2) \cdot LCM_k), m \ge 0$ , will be the same; (2) the feasibility interval of  $\Gamma_k$  is  $[t, t+LCM_k)$ , where  $t \ge O_{min}^{(k)}$ .

There are two differences between Lemma 1 and those in [12]. First, with the assumption of  $0 \le O_k < T_k$ ,  $1 \le k \le n$ , the starting point of the relevant intervals shifts to the left and is from  $O_{min}^{(k)}$  instead of from  $O_{max}^{(n)}$ , making an extended coverage of the time line. Second, Lemma 1 is feasible for all subsets  $\Gamma_k = \{\tau_1, \tau_2, ..., \tau_k\} \subseteq \Gamma_n$ ,  $1 \le k \le n$ , achieving more flexibility.

**Theorem 2.** Considering an *n*-task set  $\Gamma_n = \{\tau_1, \tau_2, ..., \tau_n\}$ using the *RM* scheduling, with a given release order such that for all  $1 \le j \le n$ ,  $0 \le O_j < T_1$ , then, for each  $2 \le k \le n$ ,  $\Gamma_k$  is schedulable if and only if: (1)  $\Gamma_{k-1} = \{\tau_1, \tau_2, ..., \tau_{k-1}\} \subseteq \Gamma_n$  is schedulable, (2) task  $\tau_k$  is schedulable in the time interval  $[O_k, O_k + max^k]$ , where  $max^k = max\{O_{min}^{\{k-1\}} + LCM_{k-1}, T_k\}$ ), and (3) there are  $j_k$  *k*-permissibility intervals for  $\tau_k$  in the time interval  $[O_k, O_k + O_{min}^{\{k-1\}} + LCM_{k-1}]$ , denoted by  $[t_1, t_2), [t_3, t_4), ..., [t_{2j_k-1}, t_{2j_k}]$ , and the next *k*-permissibility interval is denoted by  $[t_{2j_k+1}]$   $t_{2j_{k+2}}$  ), such that  $j_{k}>0$  and  $T_{k} \ge l_{max}$  or  $T_{k}=LCM_{k-1}$  when  $t_{1}-O_{k}+C_{k} \le LCM_{k-1}$  or  $T_{k} \ge l_{max}$  when  $t_{1}-O_{k}+C_{k} > LCM_{k-1}$ , where  $l_{max}=max_{i-1}^{j_{k}} \{t_{1}-O_{k}+C_{k}, t_{2i+1}-t_{2i}+2C_{k}-1\}$ .

The release order requirement in this theorem aims at getting the largest response time. Due to space limitation, we omit the proofs of Lemma 1 and Theorem 2 here; they will be included in the complete version of this paper.

### B. Computing WCRT upper bound

From Theorem 2 we may compute an *WCRT* upper bound using  $\max_{i=1}^{j_n} \{t_1 - O_n + C_n, t_{2i+1} - t_{2i} + 2C_n - 1\}$  for  $\Gamma_n$ .

This is a recursive method which can be applied step-bystep from the highest priority task to each of lower ones in the *n*-task set. Compared with the algorithms in [9]-[10], this computing-based schedulability examining method is much more efficient due to the reduction of the maximum search bound from  $LCM_n$  to  $LCM_{n-1}$ .

# IV. CONCLUSIONS AND FUTURE WORK

In this paper we present an exact condition of schedulability for P-FRP *n*-tasks using *RM* scheduling, without using the utilization bound. We reduce the maximum search bound from  $LCM_n$  to  $LCM_{n-1}$ . It is also a recursive method which can be applied to each task in the *n*-task set. Our ongoing work includes developing a *WCRT*-computing algorithm based on this condition.

### References

- C. L. Liu, L. W. Layland, "Scheduling algorithms for multiprogramming in a hard-real-time environment," Journal of ACM, 1973, 20(1): 46–61.

- [2] R. Kaiabachev, W. Taha, A. Zhu, "E-FRP with priorities," in 7th ACM & IEEE Int'l Conf. on Embedded Software(EMSOFT2007), pp.221-230.

- [3] C Belwal, A. M. K. Cheng, "A Utilization based Sufficient Condition for P-FRP," in 9th IEEE/IFIP Int'l Conf. on Embedded and Ubiquitous Computing (EUC), 2011, pp.237-242.

- [4] Z. Wan, P. Hudak, "Functional reactive programming from first principles," in ACM SIGPLAN PLDI 2000, pp. 242–252.

- J. Lehoczky, L. Sha, Y. Ding, "The rate monotonic scheduling algorithm: Exact characterization and average case behavior," IEEE RTSS 1989, pp. 166-171

- [6] N. Audsley, A. Burns, M. Richardson, K. Tindell, A. Wellings. "Applying new scheduling theory to static priority preemptive scheduling," Software Engineering Journal, 1993, 8(5): 284-292

- [7] G. Bernat, "Response time analysis of asynchronous real-time systems," Real-Time Systems, 2003, 25(2-3): 131–156.

- [8] R. I. Davis, A. Burns. "Response Time Upper Bounds for Fixed Priority Real-Time Systems," IEEE RTSS 2008, pp.407-418.

- [9] C. Belwal, A. M. K. Cheng, "Determining actual response time in P-FRP," in PADL 2011, LNCS 6539, pp. 250–264.

- [10] C. Belwal, A. M. K. Cheng, "Determining Actual Response Time in P-FRP Using Idle-Period Game Board," in 14th IEEE Int'l Symp. on Object/Component/Service-Oriented Real-Time Distributed Computing, 2011, pp. 136–143.

- [11] C. Belwal, A. M.K. Cheng, Y.F. Wen, "Time Petri nets for schedulability analysis of the transactional event handlers of P-FRP," in ACM Research in Applied Computation Symp. (RACS), 2012, pp. 257-262.

- [12] C. Belwal, A. M. K. Cheng, B. Liu, "Feasibility interval for the transactional event handlers of P-FRP," Journal of Computer and System Sciences, 2013, 79(5): 530–541.

# Concurrent soft-real-time execution on GPUs

Kiriti Nagesh Gowda, Harini Ramaprasad kiriti@siu.edu, harinir@siu.edu Southern Illinois University Carbondale

Abstract—Graphics Processing Units (GPUs) are computational powerhouses that were originally designed for accelerating graphics applications. However, in recent years, there has been a tremendous increase in support for general purpose computing on GPUs (GPGPU). GPU based architectures provide unprecedented magnitudes of computation at a fraction of the power used by traditional CPU based architectures. As real-time systems integrate more and more functionality, GPU based architectures are very attractive for their deployment. However, in a real-time system, predictability and meeting temporal requirements are much more important than raw performance. While some realtime jobs may benefit from the performance that all cores of the GPU can provide, most jobs may require only a subset of cores in order to successfully meet their temporal requirements. In this paper, we propose to study concurrent scheduling of softreal-time jobs on a GPU based platform.

Keywords GPU; Soft Real Time; Scheduling.

# I. INTRODUCTION

Real-time systems not only have to satisfy logical correctness requirements like any other computing system, but also have to adhere to temporal correctness requirements, typically represented as deadlines for every job within the system. As computational demands of such systems continue to increase in the wake of the ubiquitous presence of real-time systems in today's world, traditional single-core architectures are no longer a viable option for their deployment. As a result, there is a significant body of research that studies the challenges involved in real-time execution on multi-core architectures. However, most of this work focuses on CPU based architectures.

Recently, researchers have started to explore the use of GPU based architectures in real-time systems. There is strong motivation for enabling real-time execution on GPUs. As noted by Elliott and Anderson [1], there are two fundamental aspects that make GPUs an attractive option for real-time systems. First, GPUs execute at higher frequencies, thereby accelerating the execution of jobs allocated to it. This could improve system responsiveness. Second, the power needed for a GPU to carry out an operation is much lesser than that needed by traditional CPUs, making it ideal for use in real-time embedded systems.